Programmable Peripheral Interface (PPI) – 8255A

## CEN433 King Saud University Dr. Mohammed Amer Arafah

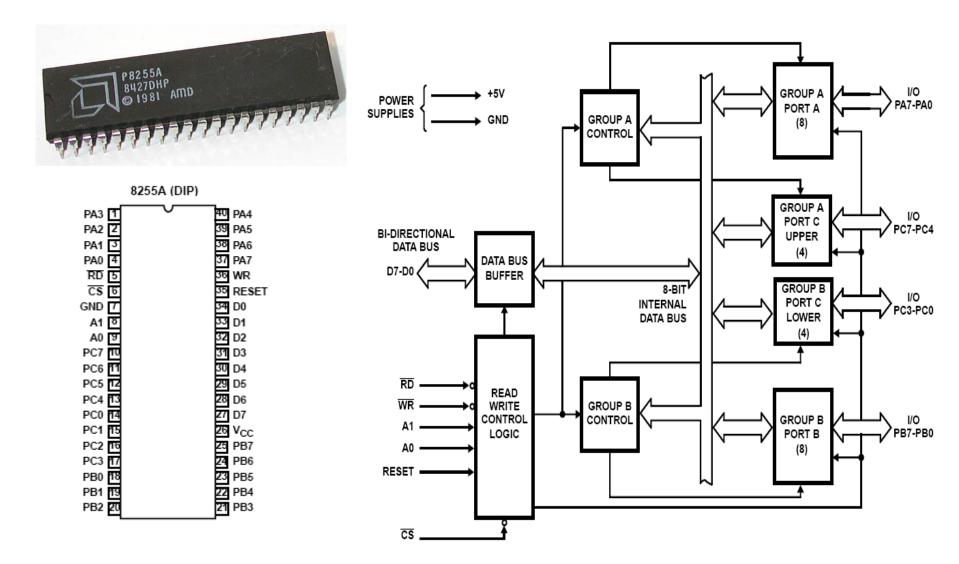

## **Functional Diagram**

# **Pin Description**

| SYMBOL  | PIN<br>NUMBER | TYPE | DESCRIPTION                                                                                                                                                                                                                                     |

|---------|---------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vcc     | 26            |      | $V_{CC}$ : The +5V power supply pin. A 0.1 $\mu F$ capacitor between pins 26 and 7 is recommended for decoupling.                                                                                                                               |

| GND     | 7             |      | GROUND                                                                                                                                                                                                                                          |

| D0-D7   | 27-34         | I/O  | DATA BUS: The Data Bus lines are bidirectional three-state pins connected to the system data bus.                                                                                                                                               |

| RESET   | 35            | I    | RESET: A high on this input clears the control register and all ports (A, B, C) are set to the input mode with the "Bus Hold" circuitry turned on.                                                                                              |

| CS      | 6             | I    | CHIP SELECT: Chip select is an active low input used to enable the 82C55A onto the Data Bus for CPU communications.                                                                                                                             |

| RD      | 5             | I    | READ: Read is an active low input control signal used by the CPU to read status information or data via the data bus.                                                                                                                           |

| WR      | 36            | I    | WRITE: Write is an active low input control signal used by the CPU to load control words and data into the 82C55A.                                                                                                                              |

| A0-A1   | 8, 9          | I    | ADDRESS: These input signals, in conjunction with the RD and WR inputs, control the selection of one of the three ports or the control word register. A0 and A1 are normally connected to the least significant bits of the Address Bus A0, A1. |

| PA0-PA7 | 1-4, 37-40    | I/O  | PORT A: 8-bit input and output port. Both bus hold high and bus hold low circuitry are present on this port.                                                                                                                                    |

| PB0-PB7 | 18-25         | I/O  | PORT B: 8-bit input and output port. Bus hold high circuitry is present on this port.                                                                                                                                                           |

| PC0-PC7 | 10-17         | I/O  | PORT C: 8-bit input and output port. Bus hold circuitry is present on this port.                                                                                                                                                                |

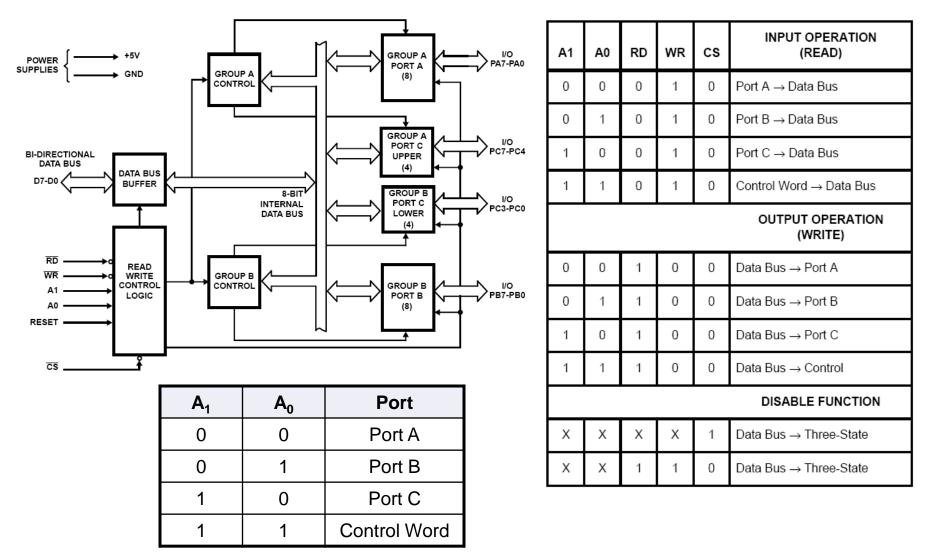

## **8255A Basic Operation**

CEN433 - King Saud University

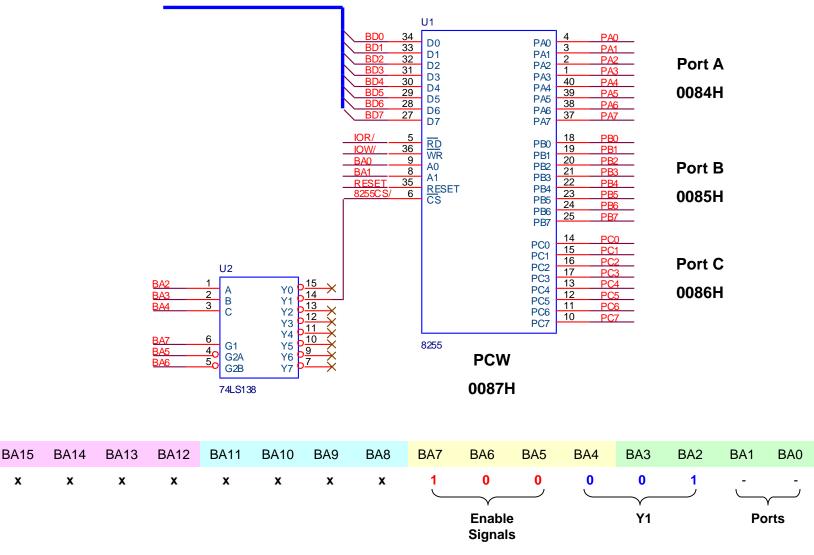

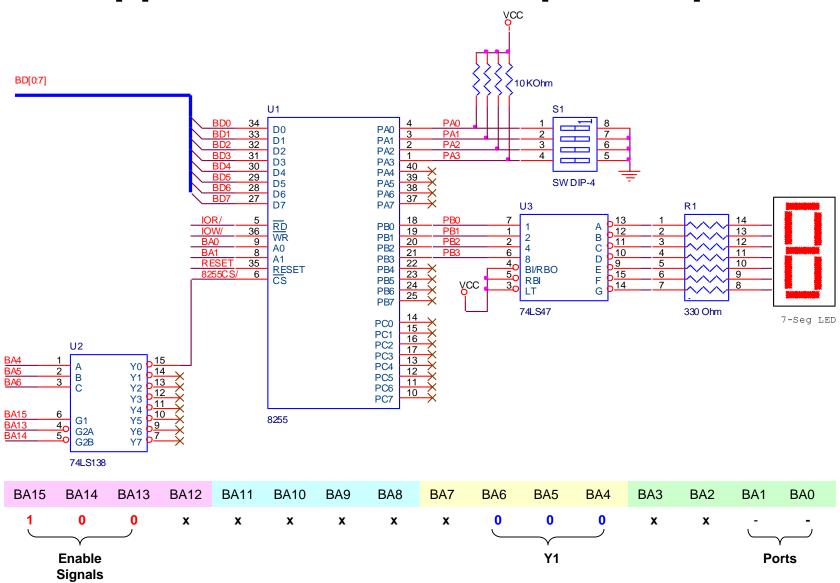

### Interfacing 8255A to Buffered 8088 System

BD[0:7]

#### Interfacing 8255A to Buffered 8086 System

BD[0:7]

CEN433 - King Saud University

**BA15**

Х

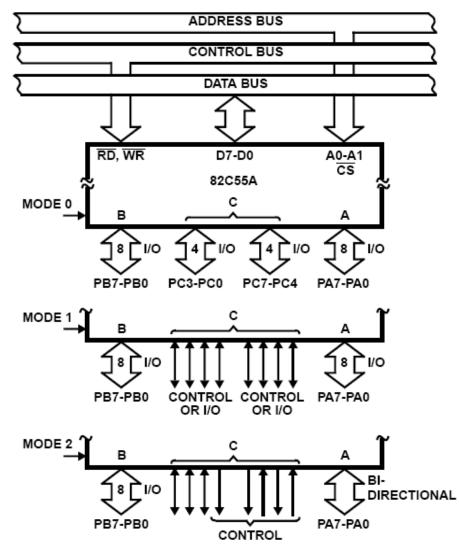

## **Mode Definitions and Bus Interface**

CEN433 - King Saud University

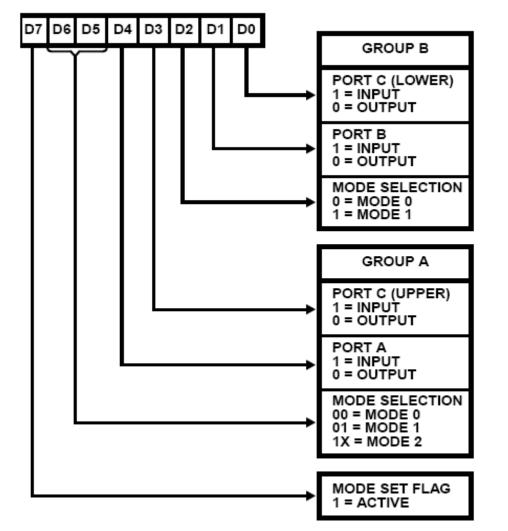

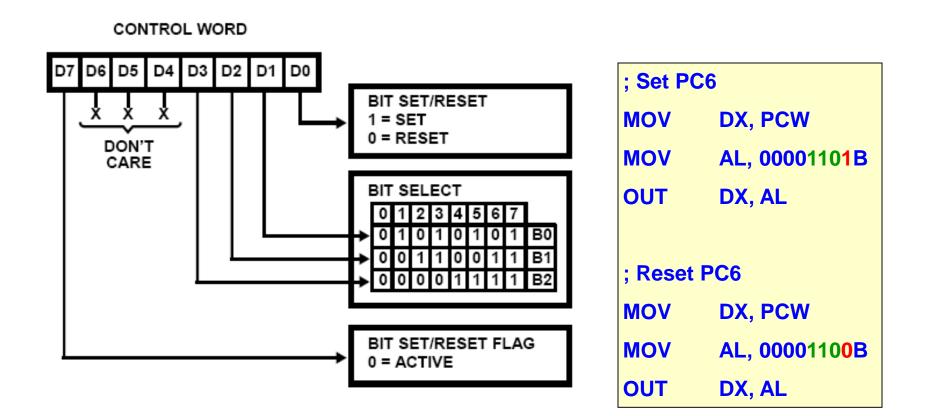

## **Mode Definition Format**

CONTROL WORD

| ; Example |               |  |  |  |  |

|-----------|---------------|--|--|--|--|

| MOV       | DX, PCW       |  |  |  |  |

| MOV       | AL, 10011001B |  |  |  |  |

| OUT       | DX, AL        |  |  |  |  |

CEN433 - King Saud University

## **Bit Set/Reset Format**

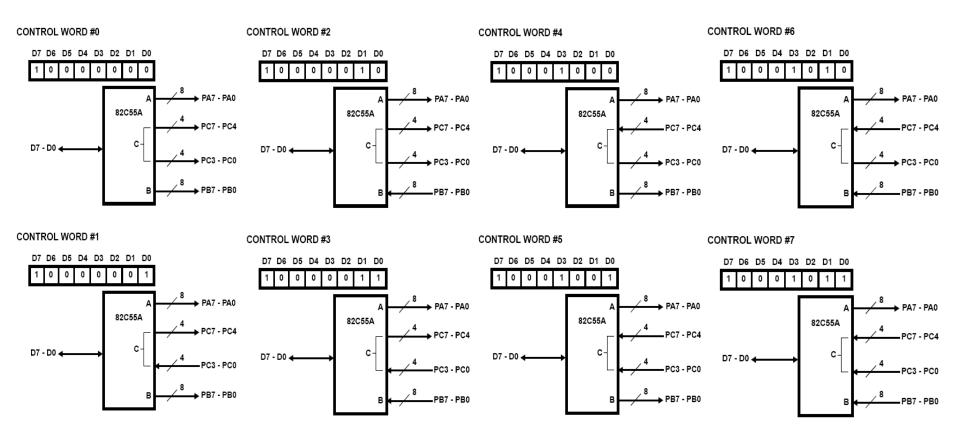

# Mode 0 (Basic Input/Output)

This functional configuration provides simple input and output operations for each of the three ports. No handshaking is required, data is simply written to or read from a specific port.

#### Mode 0 Basic Functional Definitions:

- Two 8-bit ports and two 4-bit ports.

- Any Port can be input or output.

- Outputs are latched.

- Input are not latched (tri-stated).

- 16 different Input/Output configurations possible.

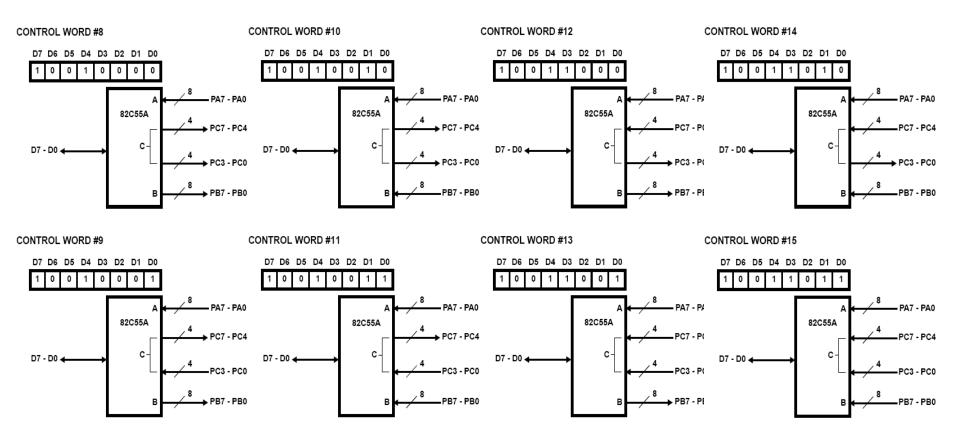

# **Mode 0 Port Definition**

| А  |    | E  | 3  | GRO    | UP A              |    | GROUP B |                  |  |

|----|----|----|----|--------|-------------------|----|---------|------------------|--|

| D4 | D3 | D1 | D0 | PORT A | PORT C<br>(Upper) | #  | PORT B  | PORTC<br>(Lower) |  |

| 0  | 0  | 0  | 0  | Output | Output            | 0  | Output  | Output           |  |

| 0  | 0  | 0  | 1  | Output | Output            | 1  | Output  | Input            |  |

| 0  | 0  | 1  | 0  | Output | Output            | 2  | Input   | Output           |  |

| 0  | 0  | 1  | 1  | Output | Output            | 3  | Input   | Input            |  |

| 0  | 1  | 0  | 0  | Output | Input             | 4  | Output  | Output           |  |

| 0  | 1  | 0  | 1  | Output | Input             | 5  | Output  | Input            |  |

| 0  | 1  | 1  | 0  | Output | Input             | 6  | Input   | Output           |  |

| 0  | 1  | 1  | 1  | Output | Input             | 7  | Input   | Input            |  |

| 1  | 0  | 0  | 0  | Input  | Output            | 8  | Output  | Output           |  |

| 1  | 0  | 0  | 1  | Input  | Output            | 9  | Output  | Input            |  |

| 1  | 0  | 1  | 0  | Input  | Output            | 10 | Input   | Output           |  |

| 1  | 0  | 1  | 1  | Input  | Output            | 11 | Input   | Input            |  |

| 1  | 1  | 0  | 0  | Input  | Input             | 12 | Output  | Output           |  |

| 1  | 1  | 0  | 1  | Input  | Input             | 13 | Output  | Input            |  |

| 1  | 1  | 1  | 0  | Input  | Input             | 14 | Input   | Output           |  |

| 1  | 1  | 1  | 1  | Input  | Input             | 15 | Input   | Input            |  |

CEN433 - King Saud University

## **Mode 0 Configurations**

## **Mode 0 Configurations**

## **Mode 0 Configurations**

Mode 0 (Basic Input)

Mode 0 (Basic Output)

CEN433 - King Saud University

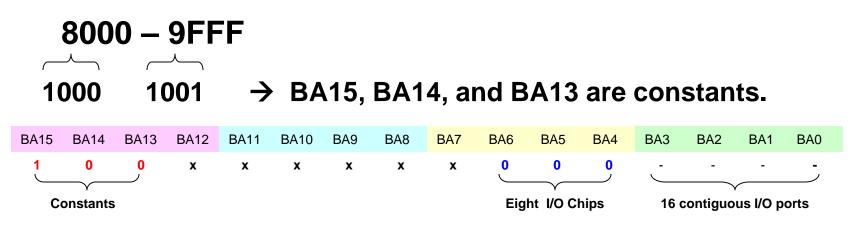

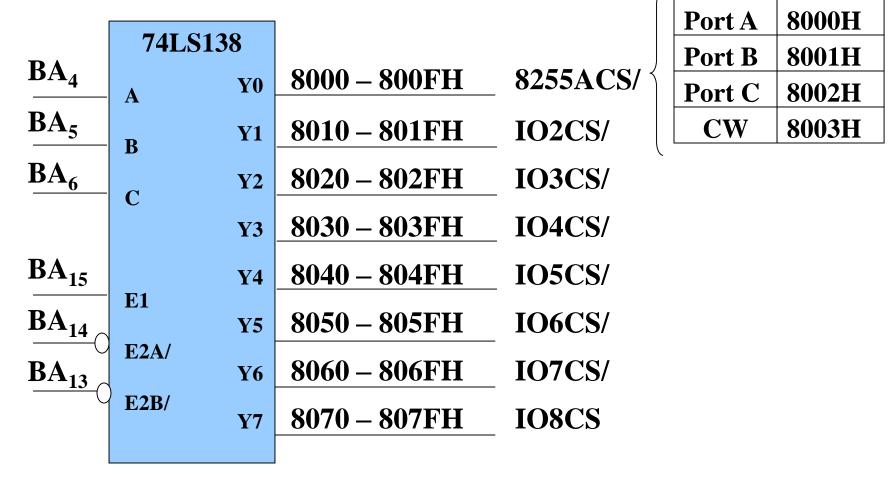

#### Example 1:

- A system has 8 I/O chips.

- The dedicated I/O space is: 8000H 9FFFH.

- Some of the I/O chips require 16 contiguous I/O ports.

Solution:

#### **Solution of Example 1:**

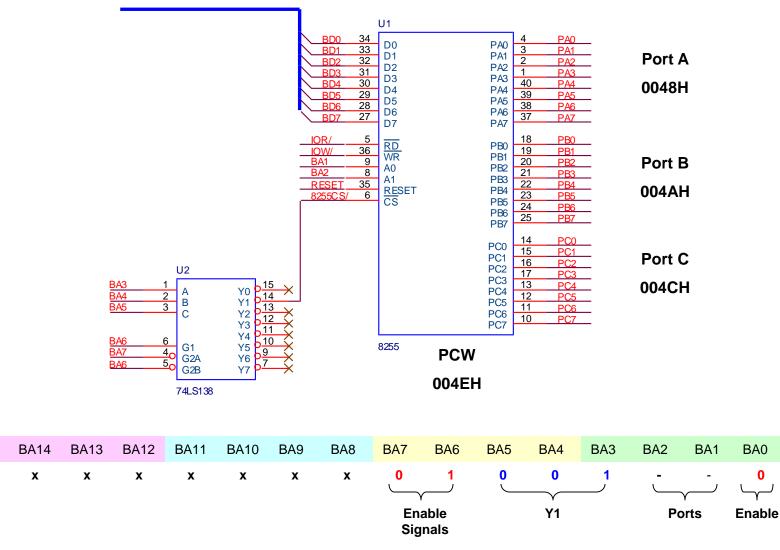

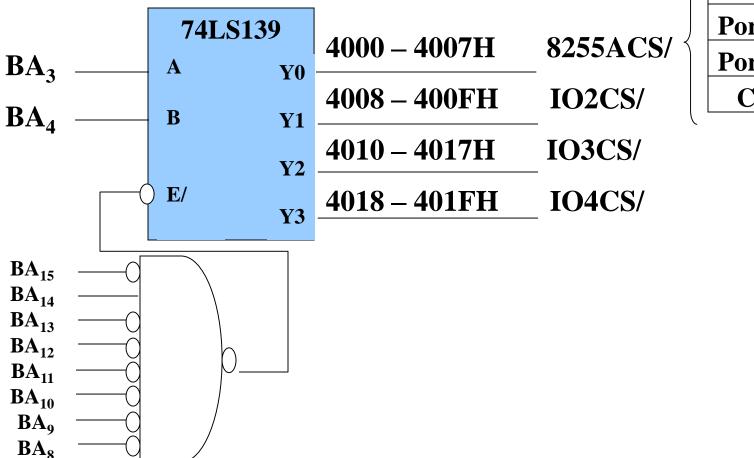

#### Example 2:

- A system has 4 I/O chips.

- The dedicated I/O space is: 4000H 40FFH.

- Some of the I/O chips require 8 contiguous I/O ports.

Solution:

4000 – 40FF

#### $\rightarrow$ BA15 – BA8 are constants.

| BA15 | BA14 | BA13 | BA12 | BA11  | BA10 | BA9 | BA8 | BA7 | BA6 | BA5 | BA4     | BA3      | BA2   | BA1      | BA0         |

|------|------|------|------|-------|------|-----|-----|-----|-----|-----|---------|----------|-------|----------|-------------|

| 0    | 1    | 0    | 0    | 0     | 0    | 0   | 0   | x   | x   | x   | 0       | <b>0</b> | -     | -        |             |

|      |      |      | Cons | tants |      |     |     |     |     |     | Four I/ | O Chips  | 8 cor | ntiguous | s I/O ports |

#### **Solution of Example 2:**

| Port A | <b>4000H</b> |

|--------|--------------|

| Port B | 4001H        |

| Port C | 4002H        |

| CW     | 4003H        |

CEN433 - King Saud University

### **Application 1: Basic Input/Output**

CEN433 - King Saud University

Mohammed Amer Arafah

19

### **Application 1: Basic Input/Output**

|            | PORTA        | EQU          | 8000H           |

|------------|--------------|--------------|-----------------|

|            | PORTB        | EQU          | 8001H           |

|            | PORTC        | EQU          | 8002H           |

|            | PCW          | EQU          | 8003H           |

| ; 8255A I  | nitializatio | n            |                 |

|            | MOV          | DX, PCW      | 7               |

|            | MOV          | AL, 1001     | 1001B           |

|            | OUT          | DX, AL       |                 |

| ; To read  | port A und   | conditional  | ly              |

| again:     | MOV          | DX, POR      | TA              |

|            | IN           | AL, DX       |                 |

| • To write | e the value  | to port R u  | inconditionally |

| , 10 1110  | INC          | DX           | inconditionally |

|            | OUT          | DX<br>DX, AL |                 |

|            |              |              |                 |

|            | JMP          | again        |                 |

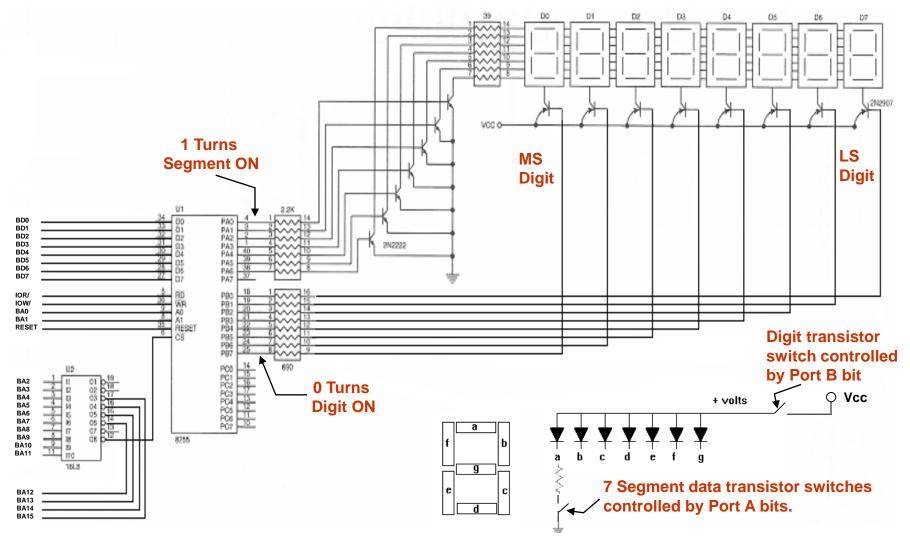

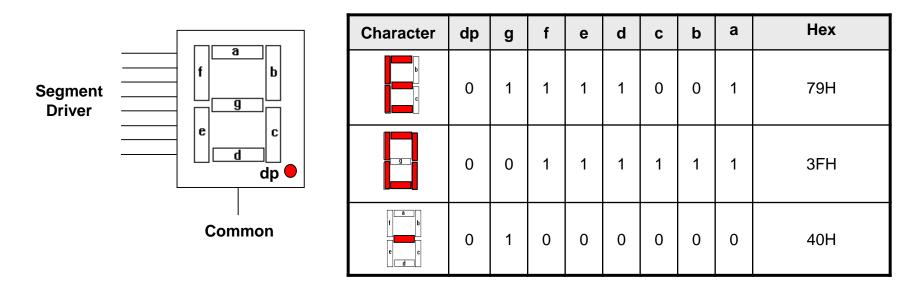

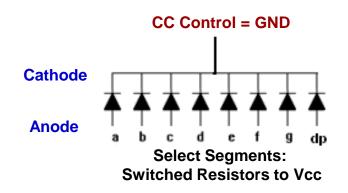

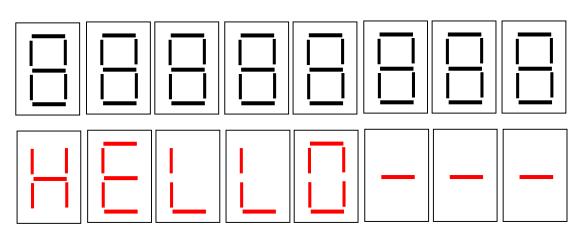

#### An 8-digit LED display interfaced to an 8088 microprocessor through 8255A

CEN433 - King Saud University

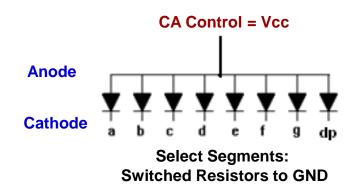

#### Two Types: Common Anode (CA)

#### **Common Cathode (CC)**

CEN433 - King Saud University

#### Address Port A<sub>0</sub> A₁ PLD Program for Address Decoding 0 0 700H Port A library ieee; Port B 701H 0 1 use ieee.std logic 1164.all; 702H Port C 1 0 entity DECODER\_11\_21 is 703H 1 1 Control Word port ( A15, A14, A13, A12, A11, A10, A9, A8, A7, A6, A5, A4, A3, A2: in STD\_LOGIC; D0: out STD LOGIC ); end; architecture V1 of DECODER 11 17 is begin A15 or A14 or A13 or A12 or A11 or not A10 D0 <= or not A9 or not A8 or A7 or A6 or A5 or A4 or A3 or A2; end V1; BA15 **BA14** BA8 **BA13** BA12 **BA11 BA10** BA9 BA7 BA6 BA5 BA4 BA3 BA2 BA1 BA0 0 0 0 0 0 1 1 1 0 0 0 0 0 0

CEN433 - King Saud University

14-bit address decoding Using PLD

Mohammed Amer Arafah

On chip

Selection

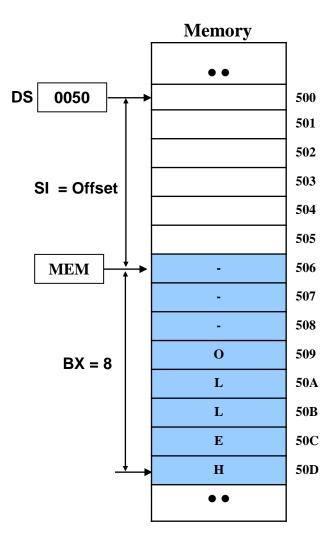

Content of the address 0050D is 'H'.

```

; Program the 82C55 for Port A and Port B are output ports in mode 0

: Address of Command Port into DX

MOV DX, 703H

MOV AL, 80H

: 80H Data into AL

OUT DX, AL ; Write 80H into Command Port to program PPI

; An assembly language procedure that multiplexes the 8-digit display.

; This procedure must be called often enough for the display to appear stable

DISP

NEAR USES AX BX DX SI

PROC

PUSHF

MOV BX, 8

;load counter BX with # of display digits

MOV AH, 01111111B

;load initial digit selection pattern to enable MS digit

MOV SI, OFFSET MEM - 1

;Load SI with offset (MEM) - 1

MOV DX, 701H

;address Port B (for Port A: decrement DX)

;Sequentially display all 8 digits starting with MS digit

.REPEAT

MOV AL, AH

OUT DX, AL; send digit selection pattern to Port B

DEC DX

;Address Port A (to send Digit Data)

MOV AL, [BX+SI]

;Load digit data from memory into AL

;send digit data to Port A

OUT DX, AL

CALL DELAY

;wait 1.0 ms leaving displayed digit ON

ROR AH, 1

adjust selection pattern to point to next digit

INC DX

;Address port B

DEC BX

;decrement counter for data of next digit.

.UNTIL BX == 0

POPF

RET

DISP

ENDP

```

| ; Delay | Loop              |                                                            |

|---------|-------------------|------------------------------------------------------------|

| DELAY   | PROC NEAR USES CX |                                                            |

|         | MOV CX, XXXX      | ; XXXX determines delay, = Delay required / loop exec time |

| D1:     |                   |                                                            |

|         | LOOP D1           |                                                            |

|         | RET               |                                                            |

| DELAY   | ENDP              |                                                            |

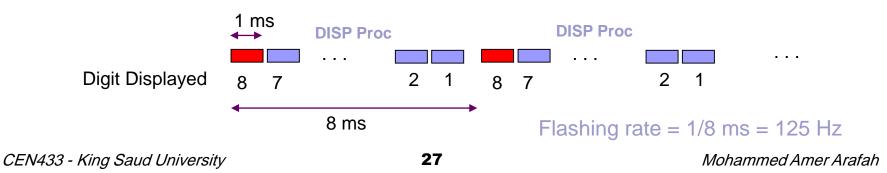

Loop execution time is calculated from instruction data and the clock frequency. An 80486 executes "LOOP D1" in 7 clock cycles With a 20 MHz clock, loop exec time = 7 x 50 = 350 ns XXXX = 1ms/350ns

#### **Display Flashing Rate:**

- Assume the DISP Procedure is called continuously

- Ignore loop execution times relative to delay time (e.g. 350 ns << 1 ms)

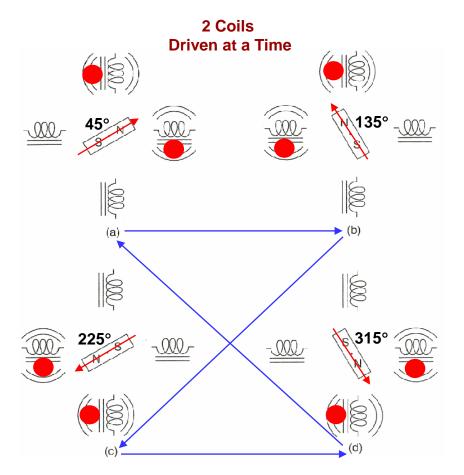

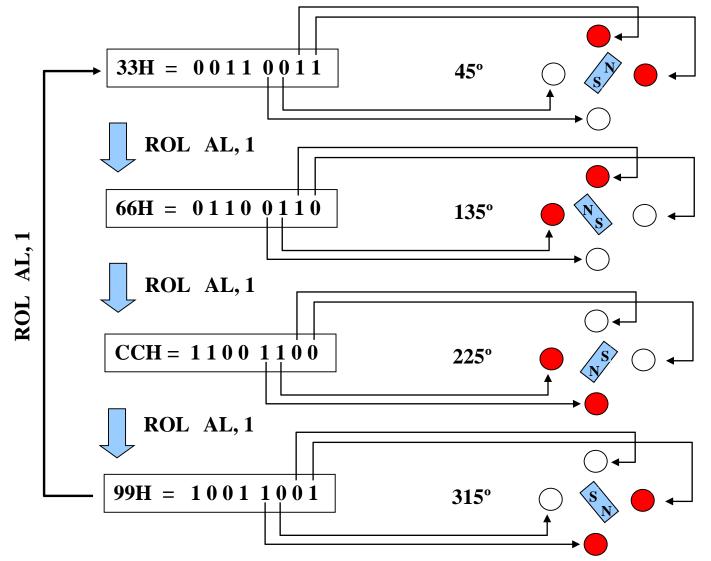

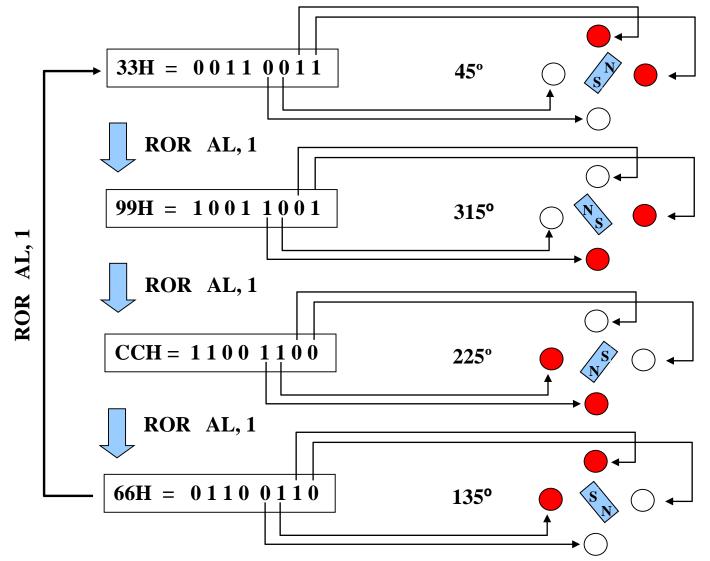

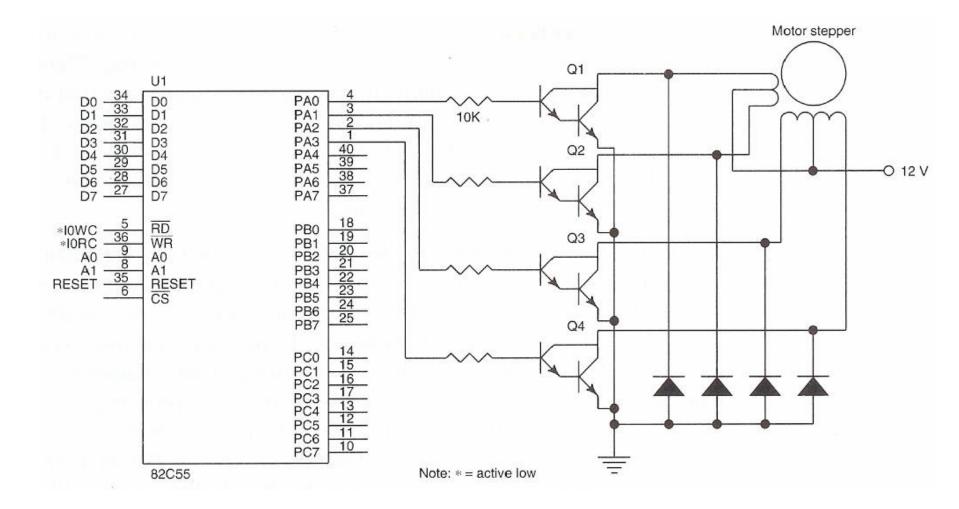

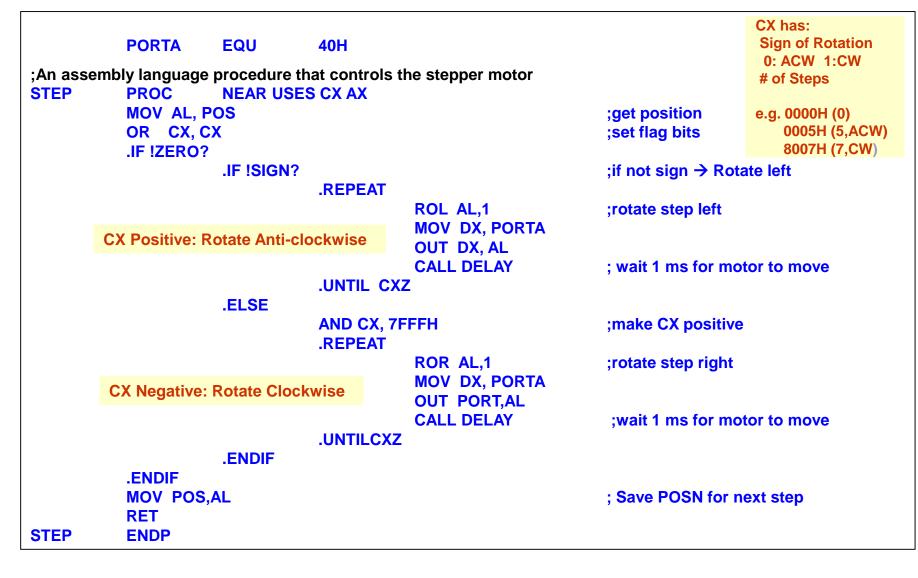

- Stepper motor is digital in nature.

- It rotates in a sequence of discrete steps controlled by sequentially energizing a set of coils (windings).

- Step angles vary from 1° to 15 ° depending on precision required (and cost)

- N Pole lies between the two energized coils

- Rotation Direction: Anti-clock wise

- Step angle: 90°

CEN433 - King Saud University

29

CEN433 - King Saud University

30

CEN433 - King Saud University

CEN433 - King Saud University

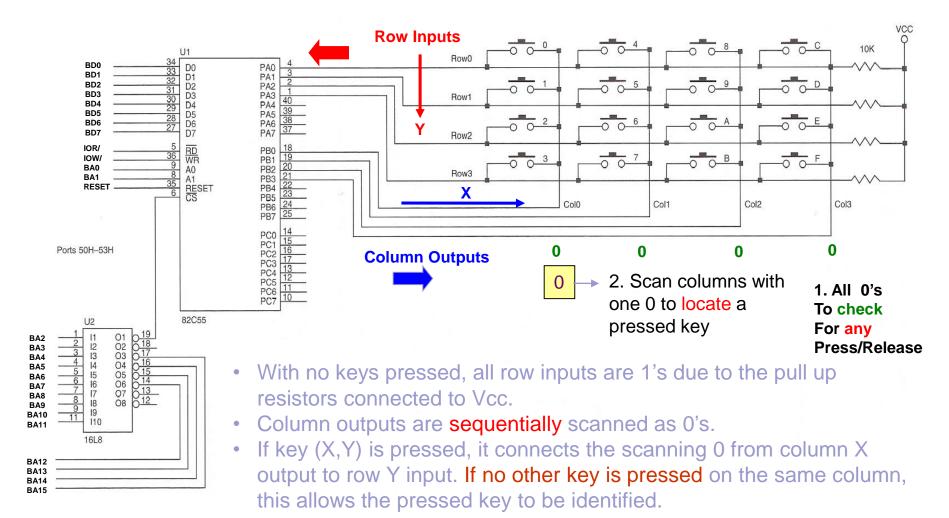

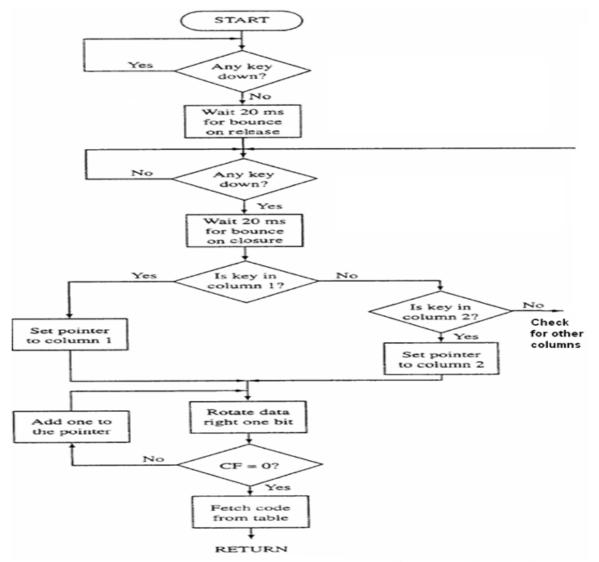

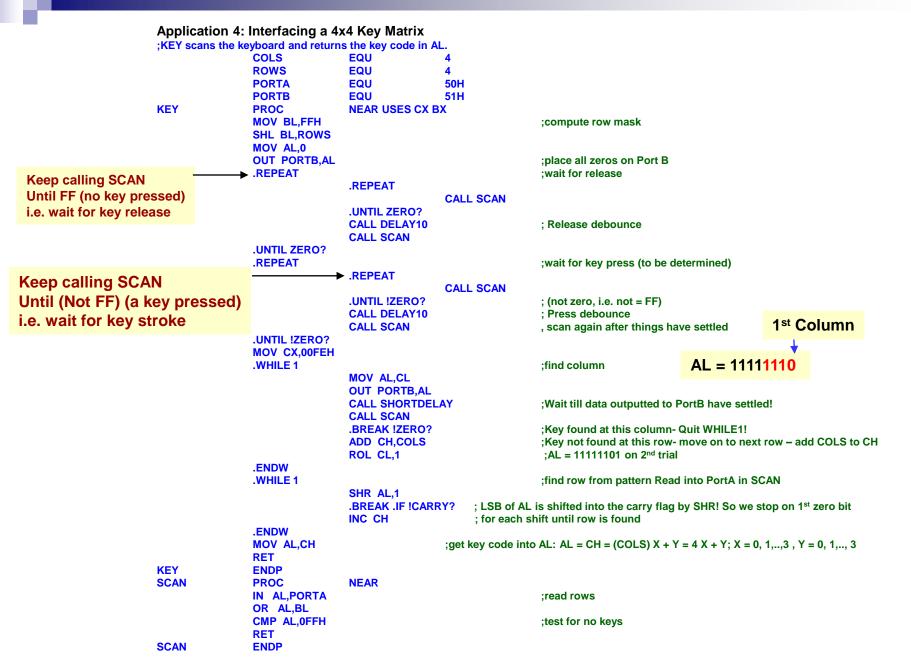

## **Application 4: Interfacing a 4x4 Key Matrix**

#### An 4 ×4 keyboard matrix interfaced to an 8088 microprocessor through 8255A

CEN433 - King Saud University

### **Application 4: Interfacing a 4x4 Key Matrix**

CEN433 - King Saud University

CEN433 - King Saud University

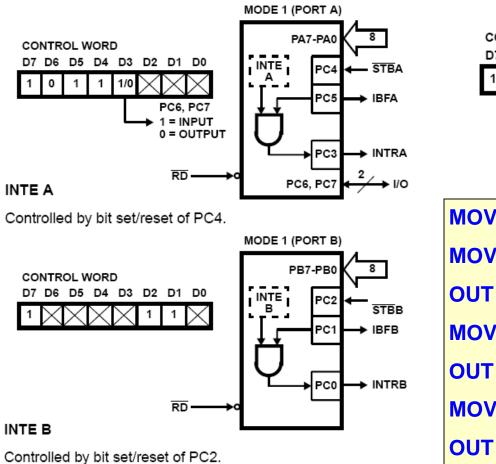

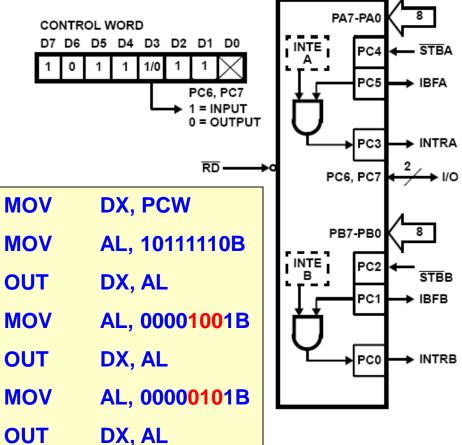

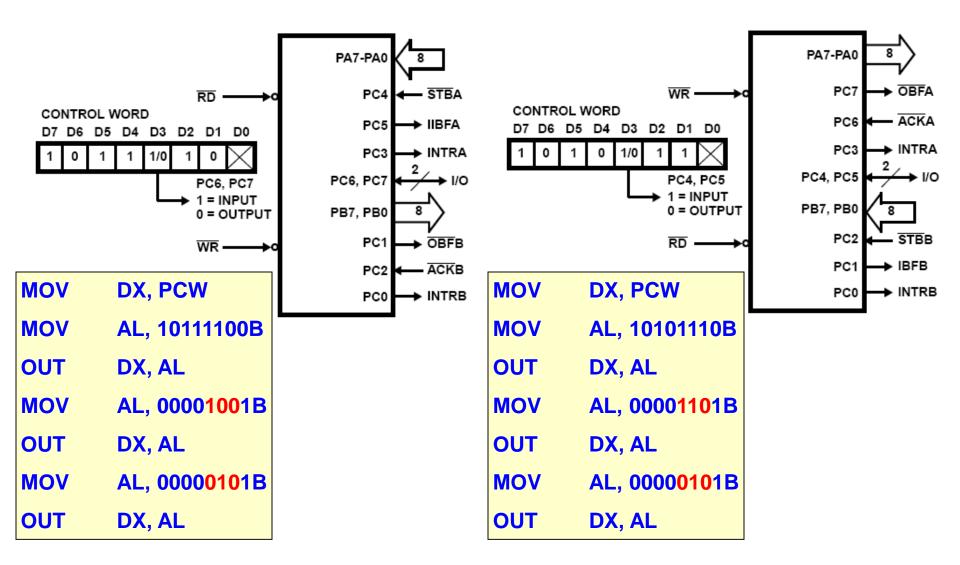

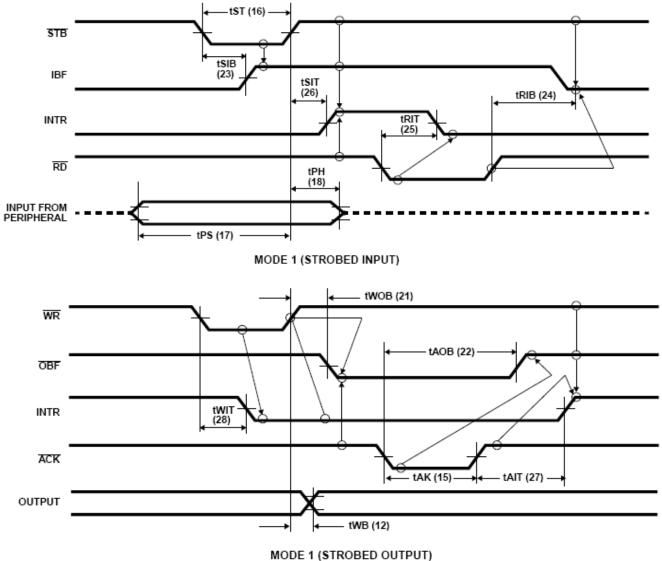

# Mode 1 (Strobed Input/Output)

- This functional configuration provides a means for transferring I/O data to or from a specified port in conjunction with strobes or "hand shaking" signals. In mode 1, port A and port B use the lines on port C to generate or accept these "hand shaking" signals.

- Mode 1 Basic Function Definitions:

- Two Groups (Group A and Group B).

- Each group contains one 8-bit port and one 5-bit (Group A) or 3-bit (Group B) control/data port.

- The 8-bit data port can be either input or output. Both inputs and outputs are latched.

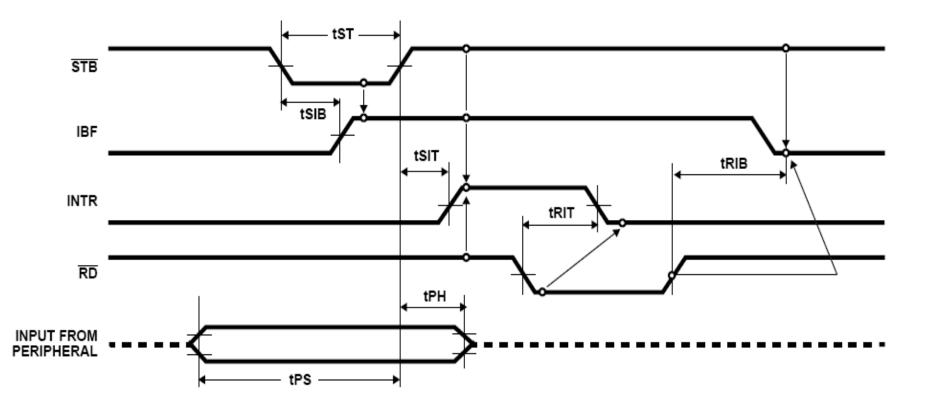

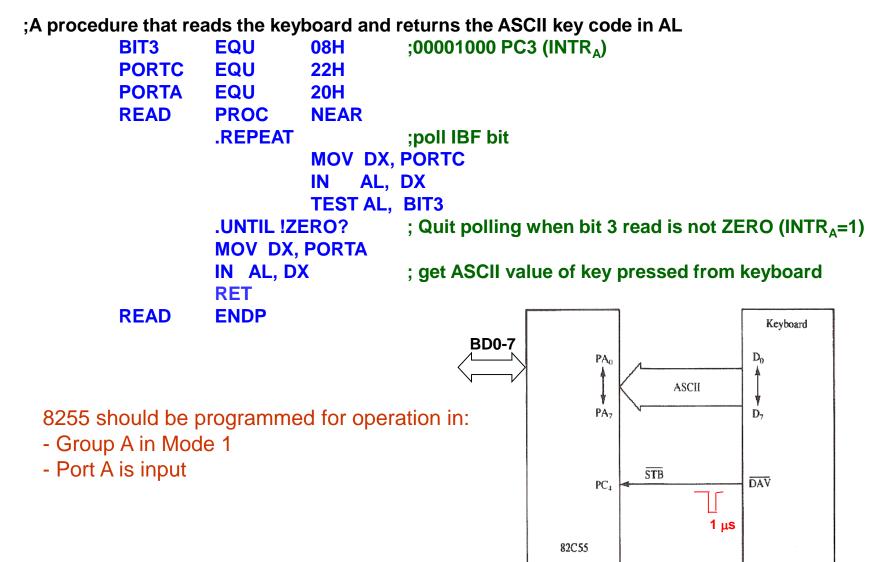

# Mode 1 (Strobed Input)

# **Input Control Signal Definition**

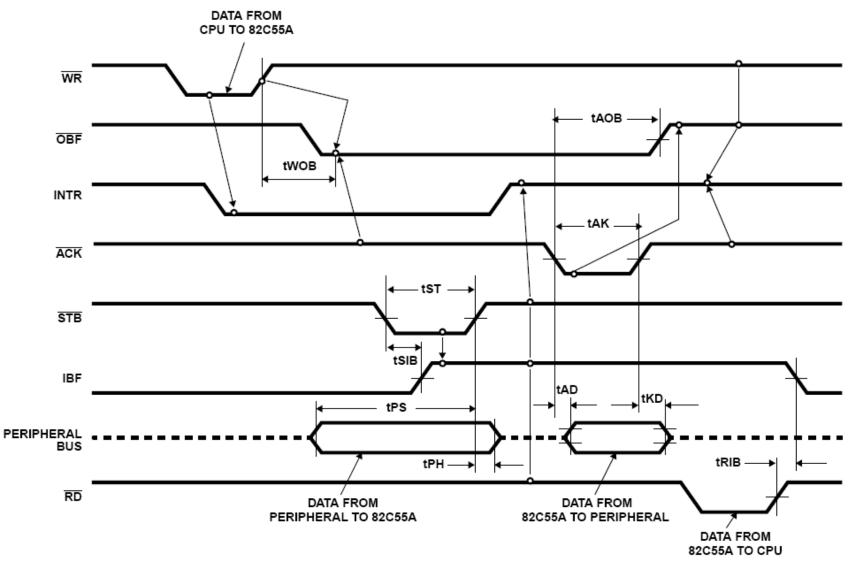

### STB (Strobe Input)

A "low" on this input loads data into the input latch.

### IBF (Input Buffer Full F/F)

A "high" on this output indicates that the data has been loaded into the input latch: in essence, and acknowledgment. IBF is set by STB input being low and is reset by the rising edge of the RD input.

### INTR (Interrupt Request)

A "high" on this output can be used to interrupt the CPU when and input device is requesting service. INTR is set by the condition: STB is a "one", IBF is a "one" and INTE is a "one". It is reset by the falling edge of RD. This procedure allows an input device to request service from the CPU by simply strobing its data into the port.

## Mode 1 (Strobed Input)

### Interfacing a Keyboard to $\mu P$ using Port A in Mode 1

CEN433 - King Saud University

40

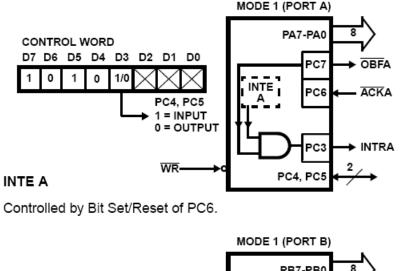

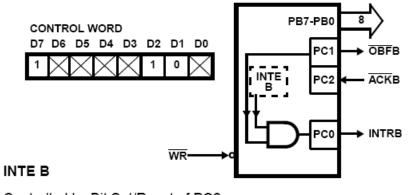

# Mode 1 (Strobed Output)

Controlled by Bit Set/Reset of PC2.

|            | 1 0 1 0 1/0 1 0<br>PC4, PC5<br>1 = INPUT<br>0 = OUTPUT |    |

|------------|--------------------------------------------------------|----|

| MOV        | DX, PCW                                                | P  |

| MOV<br>OUT | AL, 10101100B<br>DX, AL                                |    |

| MOV<br>OUT | AL, 00001101B<br>DX, AL                                | ĽС |

| MOV<br>OUT | AL, 00000101B<br>DX, AL                                |    |

CONTROL WORD

D7 D6 D5 D4 D3 D2 D1 D0

PA7-PA0

PC7

PC6

PC3

PC4. PC5

PB7-PB0

PC1

PC2

PC0

8

OBFA

- ACKA

INTRA

8

► OBFB

- ACKB

INTRB

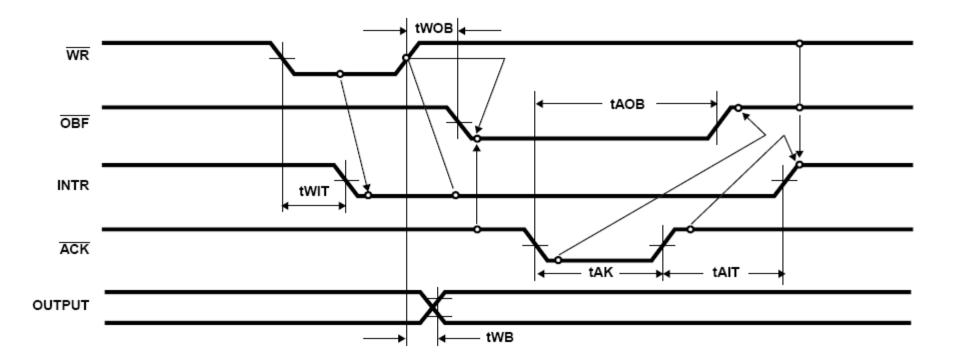

# **Output Control Signal Definition**

- OBF (Output Buffer Full F/F). The OBF output will go "low" to indicate that the CPU has written data out to be specified port. This does not mean valid data is sent out of the part at this time since OBF can go true before data is available. Data is guaranteed valid at the rising edge of OBF. The OBF F/F will be set by the rising edge of the WR input and reset by ACK input being low.

- ACK (Acknowledge Input). A "low" on this input informs the 82C55A that the data from Port A or Port B is ready to be accepted. In essence, a response from the peripheral device indicating that it is ready to accept data.

- INTR (Interrupt Request). A "high" on this output can be used to interrupt the CPU when an output device has accepted data transmitted by the CPU. INTR is set when ACK is a "one", OBF is a "one" and INTE is a "one". It is reset by the falling edge of WR.

## Mode 1 (Strobed Output)

### Interfacing a Printer to $\mu P$ using Port B in Mode 1

; A procedure that transfers an ASCII character from AH to the printer connected to port B **BITO** EQU ; Bit PC0 =  $INTR_{B}$ 1 PORTC EQU 62H PORTB EQU **61H** CMD EQU **63H** PRINT PROC **NEAR** .REPEAT ;Wait for printer ready to receive a new char- Poll INTR<sub>B</sub> till high **MOV DX. PORTC** AL, DX IN **TEST AL, BIT0** .UNTIL !ZERO? ;  $INTR_{B} = 1$  No data in output buffer, so can write into it! **MOV DX, PORTB** MOV AL, AH **OUT DX, AL**; Write ASCII char data into port latch MOV AL, 8 ;Generate data strobe pulse on PC4 **OUT CMD, AL** MOV AL, 9 82C55 Printer **OUT CMD, AL**  $PB_0$  $D_0$ RET ASCII **ENDP** PRINT 5 3 2 7 6 4 1 0 PB7 D7 **Reset PC4** 0 0 XX 0 X ACK 0 Set PC4 PC, ACK ١ſ Bit set/reset Command byte B 1 = setPC<sub>1</sub> DS 0 = resetStrobe data Selects a bit **Into Printer**

CEN433 - King Saud University

Monammed Amer Aratan

## **Combinations of Mode 1**

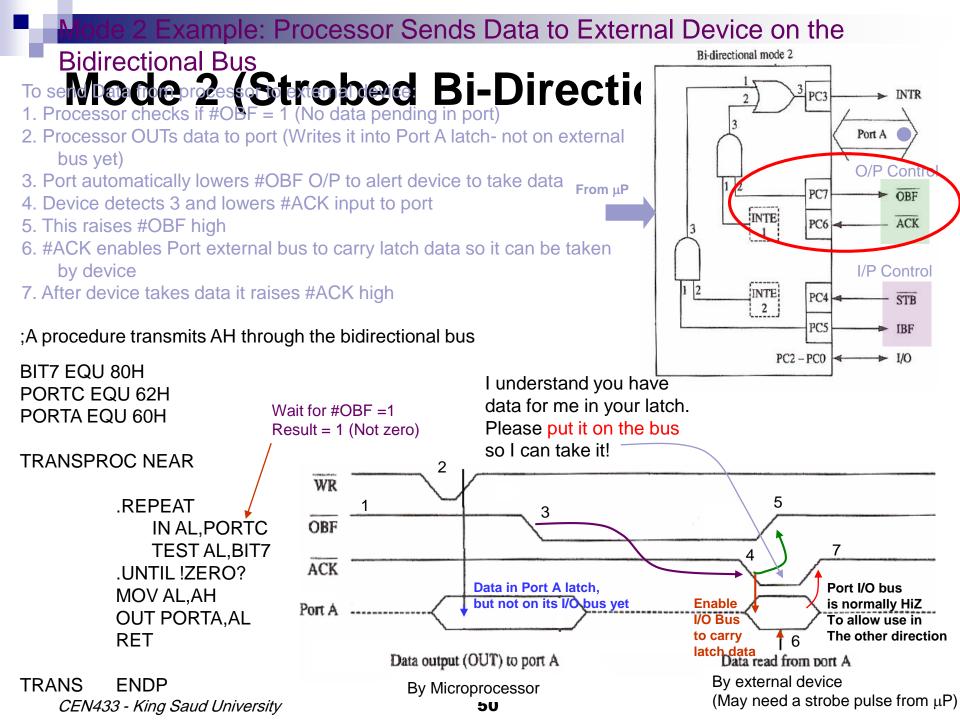

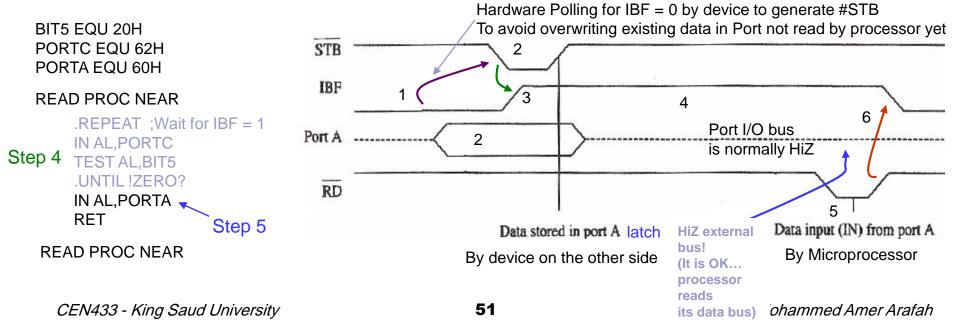

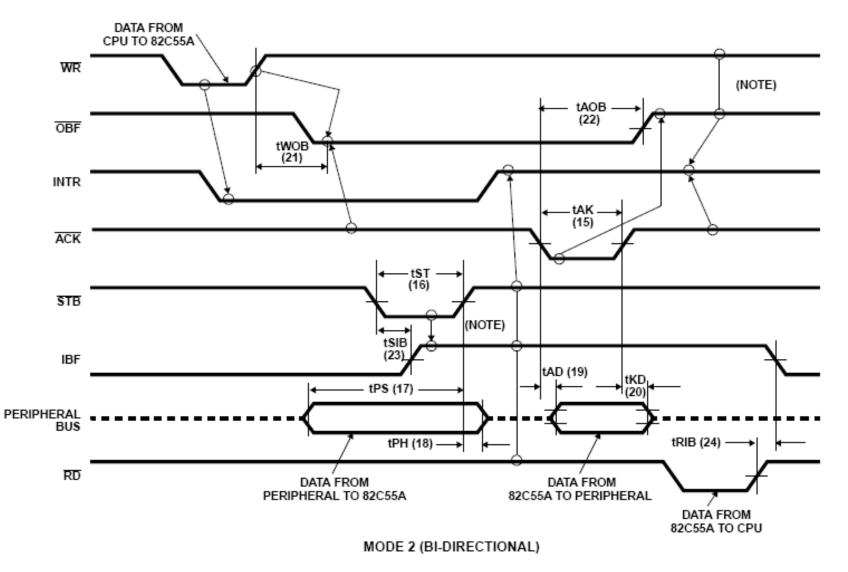

## Mode 2 (Strobed Bi-Directional Bus I/O)

- The functional configuration provides a means for communicating with a peripheral device or structure on a single 8-bit bus for both transmitting and receiving data (bidirectional bus I/O). "Hand shaking" signals are provided to maintain proper bus flow discipline similar to Mode 1. Interrupt generation and enable/disable functions are also available.

- Used in Group A only.

- One 8-bit, bi-directional bus Port (Port A) and a 5-bit control Port (Port C).

- Both inputs and outputs are latched.

- The 5-bit control port (Port C) is used for control and status for the 8-bit, bi-directional bus port (Port A).

### Mode 2 (Strobed Bi-Directional Bus I/O)

### **Bi-Directional Bus I/O Control Signal Definition**

INTR - (Interrupt Request). A high on this output can be used to interrupt the CPU for both input or output operations.

#### **Output Operations:**

- OBF (Output Buffer Full). The OBF output will go "low" to indicate that the CPU has written data out to port A.

- ACK (Acknowledge). A "low" on this input enables the three-state output buffer of port A to send out the data. Otherwise, the output buffer will be in the high impedance state.

- INTE 1 (The INTE flip-flop associated with OBF). Controlled by bit set/reset of PC4.

#### **Input Operations**

- **STB** (Strobe Input). A "low" on this input loads data into the input latch.

- IBF (Input Buffer Full F/F). A "high" on this output indicates that data has been loaded into the input latch.

- INTE 2 (The INTE flip-flop associated with IBF). Controlled by bit set/reset of PC4.

### Mode 2 (Strobed Bi-Directional Bus I/O)

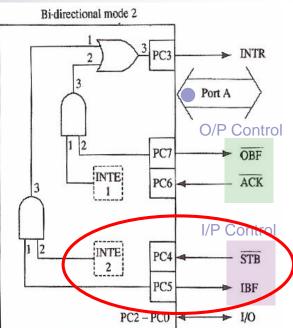

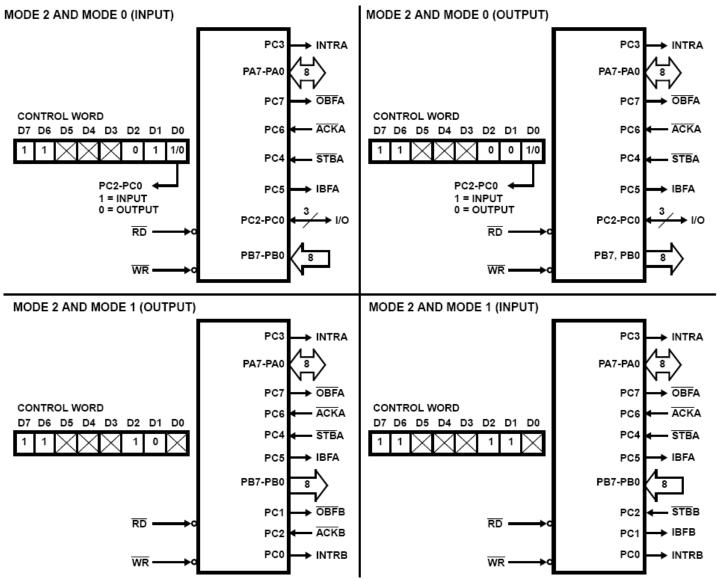

### Mode 2 Example: Processor Receives Data from External Device on

#### the Bidirectional Bus Mode 2 (Strobed Bi-Directic To Receive Data:

- 1. External device sending data checks if #IBF = 0 (No pending data in port latch not read by processor) (Hardware Polling)

- Then it puts its data on external bus and strobes it into port latch using #STB

- 3. IBF automatically goes high until data is read by processor

- 4. Processor polls IBF for IBF = 1 to make sure data is in port latch (software polling)

- 5. Processor reads data from port

- 6. This automatically lowers IBF to enable further writes

;A procedure that reads data from the bidirectional bus into AL

### **Mode 2 Combinations**

CEN433 - King Saud University

### **Mode Definition Summary**

|                                                      | МО                                     | MODE 0 MODE 1 MODE                                   |                                                              | MODE 1                                                       |                                                            | ]                             |

|------------------------------------------------------|----------------------------------------|------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------|-------------------------------|

|                                                      | IN                                     | OUT                                                  | IN                                                           | OUT                                                          | GROUP A ONLY                                               | 1                             |

| PA0<br>PA1<br>PA2<br>PA3<br>PA4<br>PA5<br>PA6<br>PA7 | In<br>In<br>In<br>In<br>In<br>In<br>In | Out<br>Out<br>Out<br>Out<br>Out<br>Out<br>Out        | In<br>In<br>In<br>In<br>In<br>In                             | Out<br>Out<br>Out<br>Out<br>Out<br>Out<br>Out                |                                                            |                               |

| PB0<br>PB1<br>PB2<br>PB3<br>PB4<br>PB5<br>PB6<br>PB7 | In<br>In<br>In<br>In<br>In<br>In<br>In | Out<br>Out<br>Out<br>Out<br>Out<br>Out<br>Out<br>Out | In<br>In<br>In<br>In<br>In<br>In<br>In                       | Out<br>Out<br>Out<br>Out<br>Out<br>Out<br>Out<br>Out         |                                                            | Mode 0<br>} or Mode 1<br>Only |

| PC0<br>PC1<br>PC2<br>PC3<br>PC4<br>PC5<br>PC6<br>PC7 | In<br>In<br>In<br>In<br>In<br>In<br>In | Out<br>Out<br>Out<br>Out<br>Out<br>Out<br>Out        | INTRB<br>IBFB<br>STBB<br>INTRA<br>STBA<br>IBFA<br>I/O<br>I/O | INTRB<br>OBFB<br>ACKB<br>INTRA<br>I/O<br>I/O<br>ACKA<br>OBFA | I/O<br>I/O<br>I/O<br>INTRA<br>STBA<br>IBFA<br>ACKA<br>OBFA |                               |

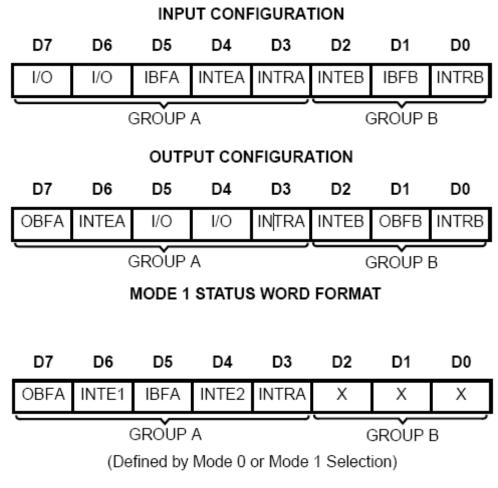

## **Status Word**

#### MODE 2 STATUS WORD FORMAT

CEN433 - King Saud University

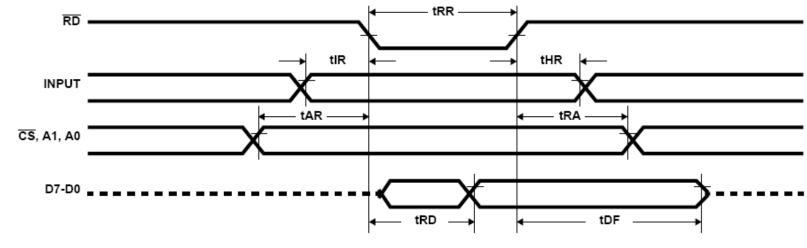

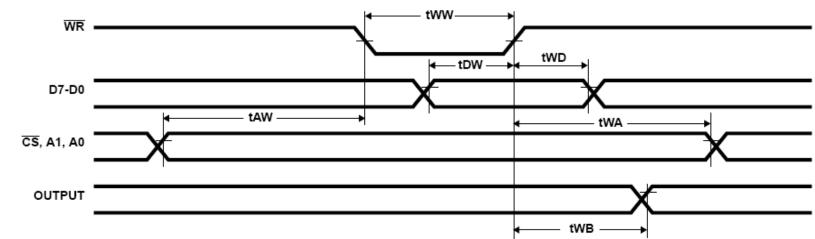

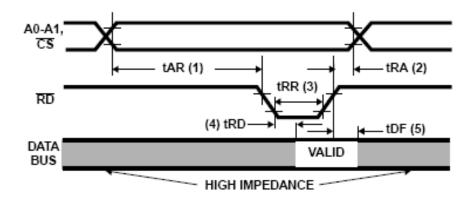

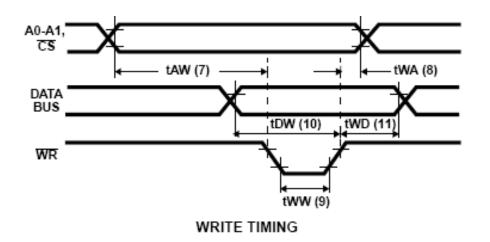

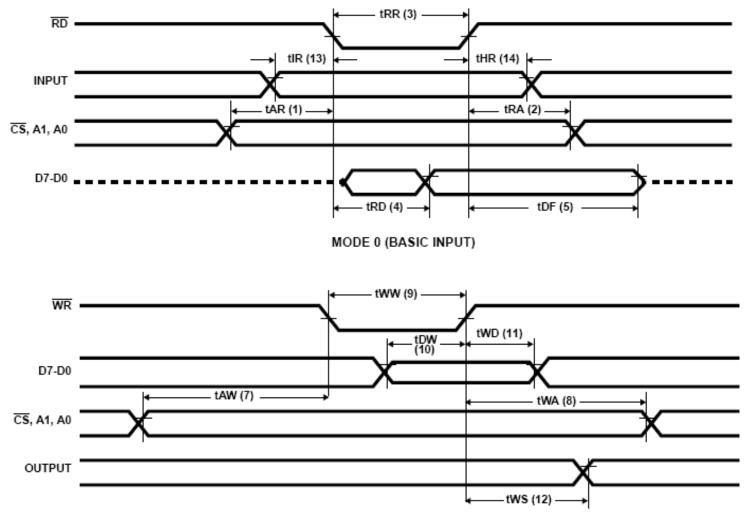

| SYMBOL         PARAMETER         MIN         MAX         MIN         MAX         UNITS         CONDITI           READ TIMING         (1) LAR         Address Stable Before RD         0         -         0         -         ns         (2) RA         Address Stable After RD         0         -         0         -         ns         (2) RA         Address Stable After RD         0         -         0         -         ns         (1) (2) RA         Address Stable After RD         0         -         100         -         100         -         100         75         100         75         ns         22         (6) RV         Time Between RDs and/or WRs         200         -         100         75         ns         (2) (3) (3) (3)         0         -         ns         (1) (3) (3) (3)         -         ns         (1) (3) (3) (3) (3) (3)         -         ns         (1) (3) (3) (3) (3) (3) (3) (3) (3) (3) (3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |                                 | 82C | 82C55A-5 |     | 82C55A |       | тгет               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------------|-----|----------|-----|--------|-------|--------------------|

| (1) 1AR         Address Stable Before RD         0         -         0         -         ns           (2) 1RA         Address Stable After RD         0         -         0         -         ns           (3) 1RR         RD Pulse Width         250         -         150         -         ns           (4) 1RD         Data Valid From RD         -         200         -         120         ns         1           (5) 1DF         Data Float After RD         10         75         10         75         ns         2           (6) 1RV         Time Between RDs and/or WRs         300         -         300         -         ns           (7) 1AW         Address Stable Before WR         0         -         0         -         ns           (9) tWW         WR Pulse Width         100         -         100         -         ns           (10) tDW         Data Valid After WR High         100         -         100         -         ns           (11) tWD         Data Valid After WR High         30         -         30         -         ns           (11) tWD         Data Valid After RD         0         -         0         -         ns <tr< th=""><th>SYMBOL</th><th>PARAMETER</th><th>MIN</th><th>MAX</th><th>MIN</th><th>MAX</th><th>UNITS</th><th>TEST<br/>CONDITIONS</th></tr<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SYMBOL       | PARAMETER                       | MIN | MAX      | MIN | MAX    | UNITS | TEST<br>CONDITIONS |

| No.         Address Stable After RD         0         -         0         -         ns           (2) tRA         Address Stable After RD         0         -         150         -         ns           (3) tRR         RD Pulse Width         250         -         150         -         ns         1           (4) tRD         Data Vaid From RD         10         75         10         75         ns         2           (6) tRV         Time Between RDs and/or WRs         300         -         300         -         ns         2           (6) tRV         Time Between RDs and/or WRs         300         -         300         -         ns         2           (7) tAW         Address Stable Before WR         0         -         0         -         ns         2           (7) tAW         Address Stable After WR         0         -         100         -         ns         2           (10) tWW         WR Pulse Width         100         -         100         -         ns         2           (11) tWD         Data Vaild After WR High         30         -         30         -         ns         1           (13) tIR         Peripheral Data After RD<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | READ TIMING  |                                 |     |          |     |        |       |                    |

| No.         No.         No.         No.         No.           (3) RR         RD Pulse Width         250         -         150         -         ns           (4) RD         Data Valid From RD         -         200         -         120         ns         1           (5) RD         Data Float After RD         10         75         10         75         ns         2           (6) RV         Time Between RDs and/or WRs         300         -         300         -         ns         -           (7) IAW         Address Stable Before WR         0         -         0         -         ns         -           (8) IWA         Address Stable After WR         20         -         20         -         ns         -           (10) IWW         WR Pulse Width         100         -         100         -         ns         -           (11) tWD         Data Valid After WR High         100         -         300         -         ns         -           (11) tWD         Data Valid After WR High         100         -         0         -         ns         -           (11) tWD         Data Before RD         0         -         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | (1) tAR      | Address Stable Before RD        | 0   | -        | 0   | -      | ns    |                    |

| Image: Constraint of the second sec | (2) tRA      | Address Stable After RD         | 0   | -        | 0   | -      | ns    |                    |

| Image: constraint of the second sec | (3) tRR      | RD Pulse Width                  | 250 | -        | 150 | -      | ns    |                    |

| Image: constraint of the set of  | (4) tRD      | Data Valid From RD              | -   | 200      | -   | 120    | ns    | 1                  |

| WRITE TIMING         Address Stable Before WR         0         -         0         -         ns           (8) tWA         Address Stable After WR         20         -         20         -         ns           (9) tWW         WR Pulse Width         100         -         100         -         ns           (10) tDW         Data Valid to WR High         100         -         100         -         ns           (11) tWD         Data Valid After WR High         30         -         30         -         ns           (11) tWD         Data Valid After WR High         30         -         30         -         ns           (12) tWB         WR = 1 to Output         -         350         -         350         ns         1           (13) tIR         Peripheral Data After RD         0         -         0         -         ns         1           (14) tHR         Peripheral Data After RD         0         -         0         -         ns         1           (15) tAK         ACK Pulse Width         100         -         100         -         ns         1           (16) tST         STB Pulse Width         100         -         100         - <td>(5) tDF</td> <td>Data Float After RD</td> <td>10</td> <td>75</td> <td>10</td> <td>75</td> <td>ns</td> <td>2</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (5) tDF      | Data Float After RD             | 10  | 75       | 10  | 75     | ns    | 2                  |

| (7) tAW         Address Stable Before WR         0         -         0         -         ns           (8) tWA         Address Stable After WR         20         -         20         -         ns           (9) tWW         WR Pulse Width         100         -         100         -         ns           (10) tDW         Data Valid to WR High         100         -         100         -         ns           (11) tWD         Data Valid After WR High         30         -         30         -         ns           (11) tWD         Data Valid After WR High         30         -         350         ns         1           (13) tIR         Peripheral Data Before RD         0         -         0         -         ns         1           (14) tHR         Peripheral Data After RD         0         -         0         -         ns         1           (15) tAK         ACK Pulse Width         100         -         100         -         ns         1           (16) tST         STB Pulse Width         100         -         100         -         ns         1           (17) tPS         Peripheral Data After STB High         20         -         20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | (6) tRV      | Time Between RDs and/or WRs     | 300 | -        | 300 | -      | ns    |                    |

| (8) tWA         Address Stable After WR         20         -         20         -         ns           (9) tWW         WR Pulse Width         100         -         100         -         ns           (10) tDW         Data Valid to WR High         100         -         100         -         ns           (11) tWD         Data Valid After WR High         30         -         30         -         ns           (11) tWD         Data Valid After WR High         30         -         30         -         ns           (11) tWD         Data Valid After WR High         30         -         30         -         ns           (11) tWD         Data Valid After WR High         30         -         30         -         ns           (11) tWD         Data Valid After WR High         30         -         30         -         ns           (13) tIR         Peripheral Data Before RD         0         -         0         -         ns           (14) tHR         Peripheral Data After RD         0         -         200         -         ns           (15) tAK         ACK Pulse Width         100         -         100         -         ns           (16) tS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | WRITE TIMING | 3                               |     |          |     |        |       |                    |

| (9) tWW         WR Pulse Width         100         -         100         -         ns           (10) tDW         Data Valid to WR High         100         -         100         -         ns           (11) tWD         Data Valid After WR High         30         -         30         -         ns           (11) tWD         Data Valid After WR High         30         -         30         -         ns           OTHER TIMING         Data Valid After WR High         30         -         350         ns         1           (13) tIR         Peripheral Data Before RD         0         -         0         -         ns         1           (14) tHR         Peripheral Data After RD         0         -         0         -         ns         1           (15) tAK         ACK Pulse Width         200         -         200         -         ns         1           (16) tST         STB Pulse Width         100         -         100         -         ns         1           (17) tPS         Peripheral Data After STB High         20         -         20         -         ns         1           (19) tAD         ACK = 0 to Output         -         175                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | (7) tAW      | Address Stable Before WR        | 0   | -        | 0   | -      | ns    |                    |

| NN         NN<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | (8) tWA      | Address Stable After WR         | 20  | -        | 20  | -      | ns    |                    |

| Image: Constraint of the second sec | (9) tWW      | WR Pulse Width                  | 100 | -        | 100 | -      | ns    |                    |

| OTHER TIMING         WR = 1 to Output         -         350         -         350         ns         1           (13) tIR         Peripheral Data Before RD         0         -         0         -         ns         1           (14) tHR         Peripheral Data After RD         0         -         0         -         ns         1           (14) tHR         Peripheral Data After RD         0         -         0         -         ns         1           (14) tHR         Peripheral Data After RD         0         -         0         -         ns         1           (15) tAK         ACK Pulse Width         200         -         200         -         ns         1           (16) tST         STB Pulse Width         100         -         100         -         ns         1           (17) tPS         Peripheral Data After STB High         20         -         20         -         ns         1           (18) tPH         Peripheral Data After STB High         50         -         175         ns         1           (19) tAD         ACK = 1 to Output Float         20         250         20         250         ns         2           (20) tKD<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | (10) tDW     | Data Valid to WR High           | 100 | -        | 100 | -      | ns    |                    |

| (12) tWB         WR = 1 to Output         -         350         -         350         ns         1           (13) tIR         Peripheral Data Before RD         0         -         0         -         ns         1           (14) tHR         Peripheral Data After RD         0         -         0         -         ns         1           (14) tHR         Peripheral Data After RD         0         -         0         -         ns         1           (15) tAK         ACK Pulse Width         200         -         200         -         ns         1           (16) tST         STB Pulse Width         100         -         100         -         ns         1           (17) tPS         Peripheral Data After STB High         20         -         20         -         ns         1           (18) tPH         Peripheral Data After STB High         50         -         50         -         ns         1           (20) tKD         ACK = 0 to Output         -         175         ns         1         1           (21) tWOB         WR = 1 to OBF = 0         -         150         -         150         ns         1           (22) tAOB <td< td=""><td>(11) tWD</td><td>Data Valid After WR High</td><td>30</td><td>-</td><td>30</td><td>-</td><td>ns</td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | (11) tWD     | Data Valid After WR High        | 30  | -        | 30  | -      | ns    |                    |

| (13) tIR         Peripheral Data Before RD         0         -         0         -         ns           (14) tHR         Peripheral Data After RD         0         -         0         -         ns           (14) tHR         Peripheral Data After RD         0         -         0         -         ns           (15) tAK         ACK Pulse Width         200         -         200         -         ns           (16) tST         STB Pulse Width         100         -         100         -         ns           (17) tPS         Peripheral Data Before STB High         20         -         20         -         ns           (18) tPH         Peripheral Data After STB High         50         -         50         -         ns           (19) tAD         ACK = 0 to Output         -         175         ns         1           (20) tKD         ACK = 1 to Output Float         20         250         20         250         ns         1           (21) tWOB         WR = 1 to OBF = 0         -         150         -         150         ns         1           (22) tAOB         ACK = 0 to IBF = 1         -         150         -         150         ns         1 <td>OTHER TIMIN</td> <td>G</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | OTHER TIMIN  | G                               |     |          |     |        |       |                    |

| (14) tHR         Peripheral Data After RD         0         -         0         -         ns           (15) tAK         ACK Pulse Width         200         -         200         -         ns         (16) tST           (16) tST         STB Pulse Width         100         -         100         -         ns         (17) tPS           Peripheral Data Before STB High         20         -         200         -         ns         (17) tPS           Peripheral Data After STB High         20         -         20         -         ns         (18) tPH           Peripheral Data After STB High         50         -         50         -         ns         (19) tAD         ACK = 0 to Output         -         175         -         175         ns         1           (20) tKD         ACK = 1 to Output Float         20         250         20         250         ns         1           (21) tWOB         WR = 1 to OBF = 0         -         150         -         150         ns         1           (22) tAOB         ACK = 0 to OBF = 1         -         150         -         150         ns         1           (23) tSIB         STB = 0 to IBF = 0         -         150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | (12) tWB     | WR = 1 to Output                | -   | 350      | -   | 350    | ns    | 1                  |

| (15) tAK         ACK Pulse Width         200         -         200         -         ns           (16) tST         STB Pulse Width         100         -         100         -         ns         (17) tPS           (17) tPS         Peripheral Data Before STB High         20         -         20         -         ns         (17) tPS           (18) tPH         Peripheral Data After STB High         50         -         50         -         ns         (19) tAD         ACK = 0 to Output         -         175         ns         1           (20) tKD         ACK = 1 to Output Float         20         250         20         250         ns         2           (21) tWOB         WR = 1 to OBF = 0         -         150         -         150         ns         1           (22) tAOB         ACK = 0 to OBF = 1         -         150         -         150         ns         1           (23) tSIB         STB = 0 to IBF = 0         -         150         -         150         ns         1           (24) tRIB         RD = 0 to INTR = 0         -         200         -         200         ns         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | (13) tIR     | Peripheral Data Before RD       | 0   | -        | 0   | -      | ns    |                    |

| (16) tST         STB Pulse Width         100         -         100         -         ns           (17) tPS         Peripheral Data Before STB High         20         -         20         -         ns           (18) tPH         Peripheral Data After STB High         50         -         50         -         ns           (19) tAD         ACK = 0 to Output         -         175         -         175         ns         1           (20) tKD         ACK = 1 to Output Float         20         250         20         250         ns         2           (21) tWOB         WR = 1 to OBF = 0         -         150         -         150         ns         1           (22) tAOB         ACK = 0 to OBF = 1         -         150         -         150         ns         1           (23) tSIB         STB = 0 to IBF = 1         -         150         -         150         ns         1           (24) tRIB         RD = 1 to IBF = 0         -         150         -         150         ns         1           (25) tRIT         RD = 0 to INTR = 0         -         200         -         200         ns         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (14) tHR     | Peripheral Data After RD        | 0   | -        | 0   | -      | ns    |                    |

| (17) H2         Peripheral Data Before STB High         20         -         20         -         ns           (18) tPH         Peripheral Data After STB High         50         -         50         -         ns           (19) tAD         ACK = 0 to Output         50         -         50         -         ns         1           (19) tAD         ACK = 0 to Output         -         175         -         175         ns         1           (20) tKD         ACK = 1 to Output Float         20         250         20         250         ns         2           (21) tWOB         WR = 1 to OBF = 0         -         150         -         150         ns         1           (22) tAOB         ACK = 0 to OBF = 1         -         150         -         150         ns         1           (23) tSIB         STB = 0 to IBF = 1         -         150         -         150         ns         1           (24) tRIB         RD = 1 to IBF = 0         -         150         -         150         ns         1           (25) tRIT         RD = 0 to INTR = 0         -         200         -         200         ns         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | (15) tAK     | ACK Pulse Width                 | 200 | -        | 200 | -      | ns    |                    |

| (18) tPH         Peripheral Data After STB High         50         -         50         -         ns           (19) tAD         ACK = 0 to Output         -         175         -         175         ns         1           (20) tKD         ACK = 1 to Output Float         20         250         20         250         ns         2           (21) tWOB         WR = 1 to OBF = 0         -         150         -         150         ns         1           (22) tAOB         ACK = 0 to OBF = 1         -         150         -         150         ns         1           (23) tSIB         STB = 0 to IBF = 1         -         150         -         150         ns         1           (24) tRIB         RD = 1 to IBF = 0         -         150         -         150         ns         1           (25) tRIT         RD = 0 to INTR = 0         -         200         -         200         ns         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | (16) tST     | STB Pulse Width                 | 100 | -        | 100 | -      | ns    |                    |

| (19) tAD       ACK = 0 to Output       -       175       -       175       ns       1         (20) tKD       ACK = 1 to Output Float       20       250       20       250       ns       2         (21) tWOB       WR = 1 to OBF = 0       -       150       -       150       ns       1         (22) tAOB       ACK = 0 to OBF = 1       -       150       -       150       ns       1         (23) tSIB       STB = 0 to IBF = 1       -       150       -       150       ns       1         (24) tRIB       RD = 1 to IBF = 0       -       150       -       150       ns       1         (25) tRIT       RD = 0 to INTR = 0       -       200       -       200       ns       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | (17) tPS     | Peripheral Data Before STB High | 20  | -        | 20  | -      | ns    |                    |

| (20) tKD         ACK = 1 to Output Float         20         250         20         250         ns         2           (21) tWOB         WR = 1 to OBF = 0         -         150         -         150         ns         1           (22) tAOB         ACK = 0 to OBF = 1         -         150         -         150         ns         1           (23) tSIB         STB = 0 to IBF = 1         -         150         -         150         ns         1           (24) tRIB         RD = 1 to IBF = 0         -         150         -         150         ns         1           (25) tRIT         RD = 0 to INTR = 0         -         200         -         200         ns         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | (18) tPH     | Peripheral Data After STB High  | 50  | -        | 50  | -      | ns    |                    |

| (21) tWOB         WR = 1 to OBF = 0         -         150         -         150         ns         1           (22) tAOB         ACK = 0 to OBF = 1         -         150         -         150         ns         1           (23) tSIB         STB = 0 to IBF = 1         -         150         -         150         ns         1           (24) tRIB         RD = 1 to IBF = 0         -         150         -         150         ns         1           (25) tRIT         RD = 0 to INTR = 0         -         200         -         200         ns         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | (19) tAD     | ACK = 0 to Output               | -   | 175      | -   | 175    | ns    | 1                  |

| Image: Normal State         ACK = 0 to OBF = 1         -         150         -         150         ns         1           (23) tSIB         STB = 0 to IBF = 1         -         150         -         150         ns         1           (24) tRIB         RD = 1 to IBF = 0         -         150         -         150         ns         1           (25) tRIT         RD = 0 to INTR = 0         -         200         -         200         ns         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | (20) tKD     | ACK = 1 to Output Float         | 20  | 250      | 20  | 250    | ns    | 2                  |

| (23) tSIB     STB = 0 to IBF = 1     -     150     -     150     ns     1       (24) tRIB     RD = 1 to IBF = 0     -     150     -     150     ns     1       (25) tRIT     RD = 0 to INTR = 0     -     200     -     200     ns     1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (21) tWOB    | WR = 1 to OBF = 0               | -   | 150      | -   | 150    | ns    | 1                  |

| (24) tRIB         RD = 1 to IBF = 0         -         150         -         150         ns         1           (25) tRIT         RD = 0 to INTR = 0         -         200         -         200         ns         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | (22) tAOB    | ACK = 0 to OBF = 1              | -   | 150      | -   | 150    | ns    | 1                  |

| (25) tRIT RD = 0 to INTR = 0 - 200 - 200 ns 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | (23) tSIB    | STB = 0 to IBF = 1              | -   | 150      | -   | 150    | ns    | 1                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | (24) tRIB    | RD = 1 to IBF = 0               | -   | 150      | -   | 150    | ns    | 1                  |