# **Memory Devices**

CEN433 King Saud University Dr. Mohammed Amer Arafah

# **Types of Memory Devices**

Two main types of memory:

#### ROM

- Read Only Memory

- Non Volatile data storage (remains valid after power off)

- For permanent storage of system software and data

- □ Can be PROM, EPROM or EEPROM (Flash) memory

#### RAM

- Random Access Memory

- □ Volatile data storage (data disappears after power off)

- □ For temporary storage of application software and data

- □ Can be SRAM (static) or DRAM (dynamic)

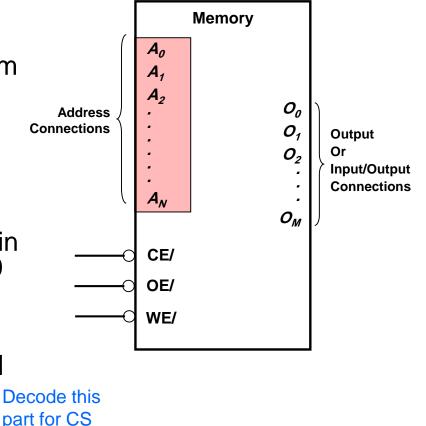

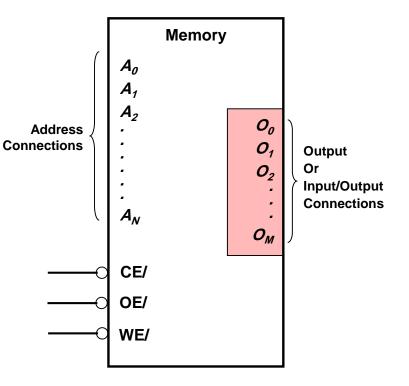

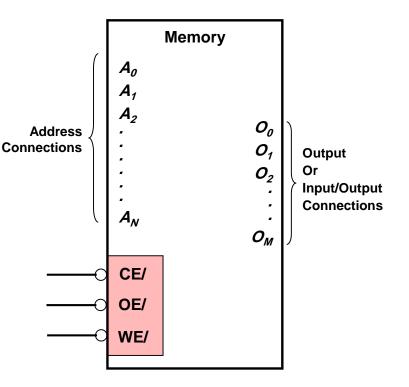

## **Memory Pin Connections**

#### Address Inputs:

- Select the required location in memory.

- Address lines are numbered from A<sub>0</sub> to as many as required to address all memory locations

- □ Example: 12-bit address:  $A_0$ - $A_{11}$ ⇒  $2^{12}$  = 4K memory locations

- Today's memory devices range in capacities upto 1G locations (30 address lines)

- Example: 4K memory: 12 bits: 000H-FFFH. e.g. from 40000H to 40FFFH.

## **Memory Pin Connections**

# Data Inputs/Outputs (RAM) Data Outputs (ROM)

- Number of lines = width of data storage, usually a byte D0-D7 (M=7)

- Wider processor data buses use multiple of such byte-wide memory devices, e.g. 64-bit

$\Rightarrow$  8 x 8-bit devices

Sometimes the total memory capacity is expressed in bits, e.g. a 64K x 8-bit = 512 Kbit

## **Memory Pin Connections**

#### Control Inputs:

- Chip Enable (CE/), or Chip Select (CS/), or simply Select (S/): Select the memory device for READ or WRITE operations.

- In addition, Indicate whether you want to READ or Write:

- READ: Enable device output for READ operations (only operation on ROMs) using OE/ or G/. If not enabled, output will be Hi-Z (floating)

- WRITE: (for RAM only) Enable device for writing using WE/ input. Should not be active simultaneously with #OE

- Some memory devices have one READ/WRITE control: R/#W

# **Memory Organization**

- Many memory device are 8-bits in width.

- A 4K x 8 memory contains 4,096 (4K) memory locations, each containing 8-bits

- A 16M x 4 memory has 16 M memory locations, each being 4-bits wide

- A 512M byte DDR\* memory card for your PC is organized as a 64M x 8 bytes. It contains eight 64M x 8 bit memory devices

\* Double Data Rate, SDRAM with data transfer at both clock edges

# **Read Only Memory Devices**

Many Types of read only memory: (Programming getting easier...)

#### ROM

- Device permanently programmed in factory by manufacturer

- □ Must be large number ( $\approx$ 10,000 pieces) to justify cost

- Once manufactured, can not be erased or reprogrammed

#### PROM

- □ **Programmable** ROM (Programmed once)

- When number of devices is too small to justify high factory programming cost

- □ Programmed in a PROM programmer that burns fuse kinks

- □ Once programmed, can not be erased for reprogramming

- □ Changes? Throw away and program another one!

## Read Only Memory Devices (Cont'd)

#### EPROM

- Erasable Programmable ROM (Programmed many)

- Used when contents need to be changed, e.g. during the development phase of a product

- □ Reprogrammed in an EPROM programmer

- Erased by exposure to UV light for say 20 minutes before reprogramming

#### EEPROM

- Electrically Erasable Programmable ROM (Programmed many ... and in situ)

- Other names: RMM (Read mostly memory), NOVRAM (Non Volatile RAM), Flash memory

- Erasing and reprogramming is made so easy (and in situ) that it can be thought of as writing (hence RAM, but with data not volatile)

- But erasing/writing takes longer time than writing into a RAM, but this is OK since it is less frequent

- Applications: BIOS, Memory for digital cameras and MP3 audio players, USB storage devices

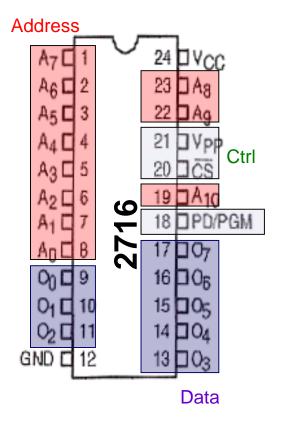

### **EPROM**

2K x 8 read only memory

1 bit + 10 bits = 11 Address inputs

8 Data outputs

Members of the 27XXXX family:

- 27<mark>04</mark> : 512 x 8

- 27<mark>08</mark> : 1K x 8

- 2716 : 2K x 8

- 27<mark>32</mark> : 4K x 8

- 27<mark>64</mark> : 8K x 8

- 27<mark>128</mark> : 16K x 8

- 27<mark>256</mark> : 32K x 8

- 27<mark>512</mark> : 64K x 8

- 27<mark>1024</mark> : 128K x 8

PIN CONFIGURATION

= Memory capacity

in K bits

### **EPROM (2764A)**

| A <sub>0</sub> -A <sub>12</sub> | Addresses     |

|---------------------------------|---------------|

| CE/                             | Chip Enable   |

| OE/                             | Output Enable |

| O <sub>0</sub> -O <sub>7</sub>  | Outputs       |

| PGM/                            | Program       |

| N.C.                            | Not Connected |

| 27512      | 27256      | 27128          | 2764           | 2732           | 2716           | E | PI | २० | М |   | 2716        | 2732  | 2764 | 27128         | 27256       | 27512              |

|------------|------------|----------------|----------------|----------------|----------------|---|----|----|---|---|-------------|-------|------|---------------|-------------|--------------------|

| Å15        | Vpp        | Vpp            | Vpp            |                |                | ٥ |    | ァ  |   | þ |             |       | Vcc  | Vcc           | Ycc         | Vcc                |

| A12        | A12        | A12            | A12            |                |                |   |    |    |   |   |             |       | PGM  | PGM           | Ан          | Ан                 |

| Å۶         | Å۶         | Å۶             | Å۶             | Å۶             | Å۶             | ٥ | 乀  | ノ  |   |   | Ycc         | Vcc   | N.C. | <b>Å</b> 13   | <b>A</b> 13 | <b>A</b> 13        |

| Å۶         | Å۶         | Å۶             | Å۶             | Å۶             | Å۶             |   |    |    |   |   | A۵          | ٨٥    | Å۵   | A٥            | A٥          | A٥                 |

| Å٥         | Å٥         | A٥             | Å٥             | Å٥             | Å٥             |   |    |    |   |   | A۹          | Å۹    | Å۹   | Å۶            | Å۶          | A۹                 |

| A4         | A4         | A4             | A4             | A4             | A4             |   |    |    |   |   | Vpp         | Ă۱    | Ă۱   | ٨n            | Ăıı         | Аn                 |

| Å٥         | Å٥         | Å٥             | Å٥             | Å٥             | Å٥             |   |    |    |   |   | <b>OE</b> V | 'pp/0 | E OE | <del>de</del> | <b>OE</b> N | /pp/ <del>OE</del> |

| A2         | A2         | Å2             | A2             | A2             | Å2             |   |    |    |   |   | A10         | A10   | A10  | A10           | A10         | A10                |

| Å1         | A1         | Å1             | Å1             | A1             | Å1             |   |    |    |   |   | Œ           | Œ     | CE   | Œ             | Œ           | Œ                  |

| A٥         | Å٥         | A٥             | A٥             | ٨o             | A٥             |   |    |    |   |   | D۲          | D7    | D۲   | D7            | D۲          | D۷                 |

| D.         | D٥         | D٥             | D٥             | D٥             | D٥             |   |    |    |   |   | De          | De    | De   | De            | De          | De                 |

| D1         | <b>D</b> 1 | $\mathbf{D}_1$ | $\mathbf{D}_1$ | $\mathbf{D}_1$ | $\mathbf{D}_1$ |   |    |    |   |   | D₅          | D₅    | D₅   | D5            | D₅          | D₅                 |

| <b>D</b> 2 | <b>D</b> 2 | D 2            | <b>D</b> 2     | <b>D</b> 2     | <b>D</b> 2     |   |    |    |   |   | D4          | D4    | D4   | D4            | D4          | D4                 |

| GND        | GND        | GND            | GND            | GND            | GND            |   |    |    |   |   | D₃          | D₃    | D₃   | Dō            | Dō          | D₅                 |

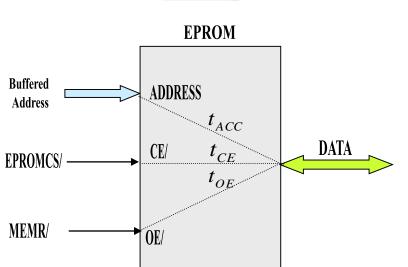

### **EPROM Timing Parameters**

2764 4

| 27512<br>27C512 | 27256<br>27C256 | 27128A<br>27C128 | 2732A          | 2716           |

|-----------------|-----------------|------------------|----------------|----------------|

| A <sub>15</sub> | VPP             | Vpp              |                |                |

| A12             | A12             | A12              |                |                |

| A7              | A7              | A7               | A7             | A7             |

| A <sub>6</sub>  | A6              | A6               | A <sub>6</sub> | A6             |

| A5              | A5              | A5               | A5             | A5             |

| A4              | A4              | A4               | A4             | A4             |

| Ag              | A3              | A3               | A3             | A3             |

| A <sub>2</sub>  | A <sub>2</sub>  | A2               | A <sub>2</sub> | A <sub>2</sub> |

| A1              | A1              | A1               | A1             | A <sub>1</sub> |

| A_0             | A0              | A0               | Λ0             | Ao             |

| O <sub>0</sub>  | O0              | 00               | 00             | 00             |

| 01              | O1              | 0,               | 01             | 01             |

| 02              | 02              | 02               | 02             | 02             |

| GND             | GND             | GND              | GND            | GND            |

|                                                                              |   | 2/04                | A  |    |                                                             |

|------------------------------------------------------------------------------|---|---------------------|----|----|-------------------------------------------------------------|

| Ver                                                                          | ď | $\overline{\gamma}$ | 28 | Ь  | Vcc                                                         |

| Vpp<br>Å <sub>12</sub><br>Å <sub>7</sub><br>Å <sub>6</sub><br>Å <sub>5</sub> | d | 2                   | 27 | Ь  | PGM                                                         |

| ۸,                                                                           | d | 3                   | 26 | Þ  | N.C.                                                        |

| A6                                                                           | q | 4                   | 25 | Þ  | A.                                                          |

| ۸,                                                                           | q | 5                   | 24 | Þ  | <b>A</b> 9                                                  |

| A.<br>A.<br>A.<br>A.<br>A.<br>A.<br>Ou                                       | q | 6                   | 23 | Þ. | A.,                                                         |

| ٨.                                                                           | q | 7                   | 55 | Þ  | ŌĒ                                                          |

| A2                                                                           | q | •                   | 21 | Ρ  | A10                                                         |

| Α,                                                                           | 9 | 9                   | 20 | Р  | CE                                                          |

| A.,                                                                          |   | 10                  | 19 | Ρ  | ο,                                                          |

| 0.                                                                           | 9 | 11                  | 10 | P  | 06                                                          |

| σ,                                                                           | 9 | 12                  | 17 | Р  | ο,                                                          |

| 0,<br>0,<br>GND                                                              | 9 | 13                  | 16 | E  | PGM<br>N.C.<br>As<br>As<br>CE<br>OF<br>OS<br>OS<br>OS<br>OS |

| GND                                                                          | Ч | 14                  | 15 | P  | 03                                                          |

|   | 2716            | 2732A           | 27128A<br>27G128 | 27256<br>27C256 | 27512<br>27C512 |        |

|---|-----------------|-----------------|------------------|-----------------|-----------------|--------|

|   |                 |                 | Vcc              | Voc             | Vcc             |        |

|   |                 |                 | PGM              | A14             | A <sub>14</sub> |        |

|   | Vcc             | Vcc             | A13              | A13             | A <sub>13</sub> |        |

|   | A <sub>8</sub>  | Ae              | AB               | A <sub>8</sub>  | Ae              |        |

|   | Ag              | Ag              | Ag               | Ag              | Ag              |        |

|   | VPP             | A <sub>11</sub> | A11              | A11             | A <sub>11</sub> |        |

| < | ŌE              | OE/Vpp          | ŌĒ               | ŌĒ              | DE/Vpp          | $\geq$ |

|   | A <sub>10</sub> | A <sub>10</sub> | A <sub>10</sub>  | A <sub>10</sub> | A <sub>10</sub> |        |

| < | ĈĒ              | CE              | CE               | ĈĒ              | CE              | $\geq$ |

|   | 07              | 07              | 07               | 07              | 07              |        |

|   | 06              | 06              | O <sub>6</sub>   | 06              | O <sub>6</sub>  |        |

|   | 05              | 05              | O5               | Q5              | 05              |        |

|   | 04              | 0₄              | O4               | 04              | 04              |        |

|   | 03              | O3              | O3               | O3              | O3              |        |

CEN433 - King Saud University

Mohammed Amer Arafah

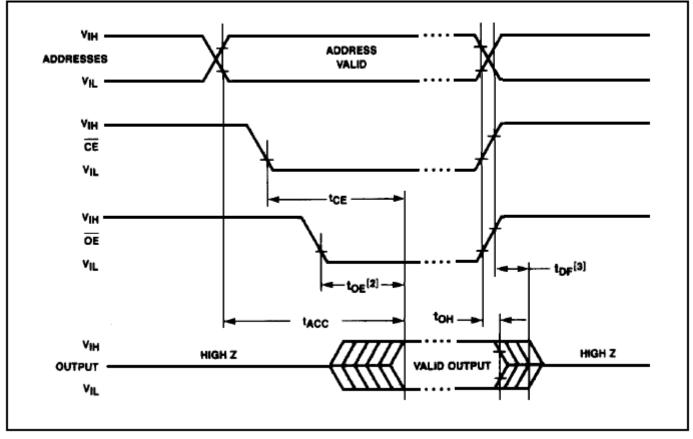

### **EPROM Timing Parameters (2764A)**

#### A.C. WAVEFORMS

## **EPROM Timing Parameters (2764A)**

#### **READ OPERATION**

#### D.C. CHARACTERISTICS $0^{\circ}C \leq T_{\mbox{A}} \leq +70^{\circ}C$

| Symbol                         | Parameter                       |      | Limits              | Conditions |                                         |

|--------------------------------|---------------------------------|------|---------------------|------------|-----------------------------------------|

|                                |                                 | Min  | Max                 | Unit       | conditions                              |

| lu                             | Input Load Current              |      | 10                  | μA         | V <sub>IN</sub> = 0V to V <sub>CC</sub> |

| ILO                            | Output Leakage Current          |      | 10                  | μΑ         | $V_{OUT} = 0V \text{ to } V_{CC}$       |

| Ipp <sup>(2)</sup>             | V <sub>PP</sub> Current Read    |      | 5                   | mA         | V <sub>PP</sub> = 5.5V                  |

| I <sub>SB</sub>                | V <sub>CC</sub> Current Standby |      | 35                  | mA         | <u>CE</u> ≃ V <sub>IH</sub>             |

| ICC <sup>(2)</sup>             | V <sub>CC</sub> Current Active  |      | 75                  | mA         | CE = OE = V <sub>IL</sub>               |

| V <sub>IL</sub>                | Input Low Voltage               | -0.1 | + 0.8               | v          |                                         |

| VIH                            | Input High Voltage              | 2.0  | V <sub>CC</sub> + 1 | v          |                                         |

| VOL                            | Output Low Voltage              |      | 0.45                | v          | l <sub>OL</sub> = 2.1 mA                |

| V <sub>OH</sub>                | Output High Voltage             | 2.4  |                     | v          | İ <sub>OH</sub> ≂ −400 µA               |

| V <sub>PP</sub> <sup>(2)</sup> | V <sub>PP</sub> Read Voltage    | 3.8  | V <sub>CC</sub>     | v          | $V_{CC} = 5.0V \pm 0.25V$               |

#### A.C. CHARACTERISTICS $0^{\circ}C \leq T_{\text{A}} \leq \,+\,70^{\circ}C$

| Versions(4)                    | V <sub>CC</sub> ± 5%                                                    | 276 | 4A-1 | 2764 | 4A-2 | 276  | i4A      |    | Test                                     |

|--------------------------------|-------------------------------------------------------------------------|-----|------|------|------|------|----------|----|------------------------------------------|

|                                | V <sub>CC</sub> ± 10%                                                   |     |      | 2764 | A-20 | 2764 | 2764A-25 |    | Conditions                               |

| Symbol                         | Parameter                                                               | Min | Max  | Min  | Max  | Min  | Max      |    |                                          |

| tacc                           | Address to<br>Output Delay                                              |     | 180  |      | 200  |      | 250      | ns | $\overline{CE} = \overline{OE} = V_{IL}$ |

| <sup>t</sup> CE                | CE to Output<br>Delay                                                   |     | 180  |      | 200  |      | 250      | ns | $\overline{OE} = V_{IL}$                 |

| <sup>t</sup> OE                | OE to Output<br>Delay                                                   |     | 65   |      | 75   |      | 100      | ns | ĈË = V <sub>IL</sub>                     |

| t <sub>DF</sub> <sup>(3)</sup> | OE High to<br>Output Float                                              | 0   | 55   | 0    | 55   | 0    | 60       | ns | $\overline{CE} = V_{IL}$                 |

| l <sub>OH</sub> (3)            | Output Hold<br>from Address,<br>CE or OE<br>Whichever<br>Occurred First | 0   |      | 0    |      | 0    |          | ns | CE = OE = VIL                            |

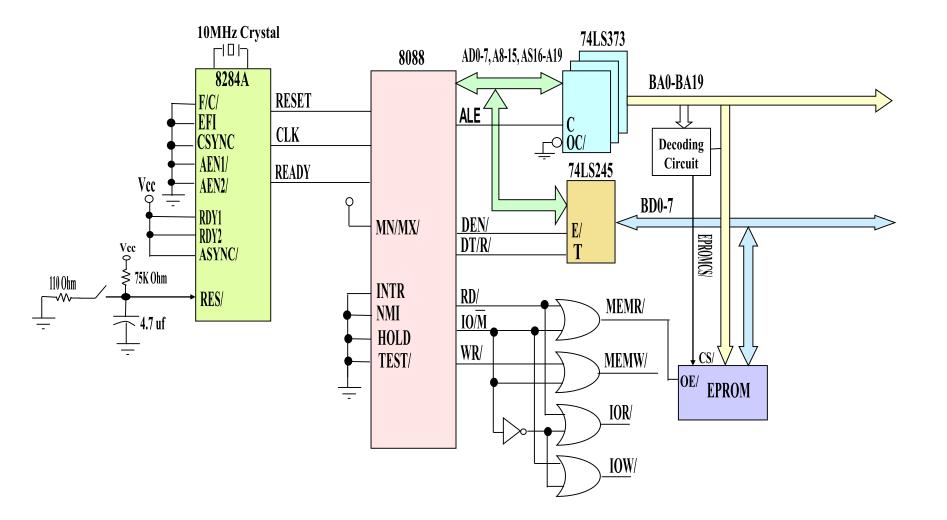

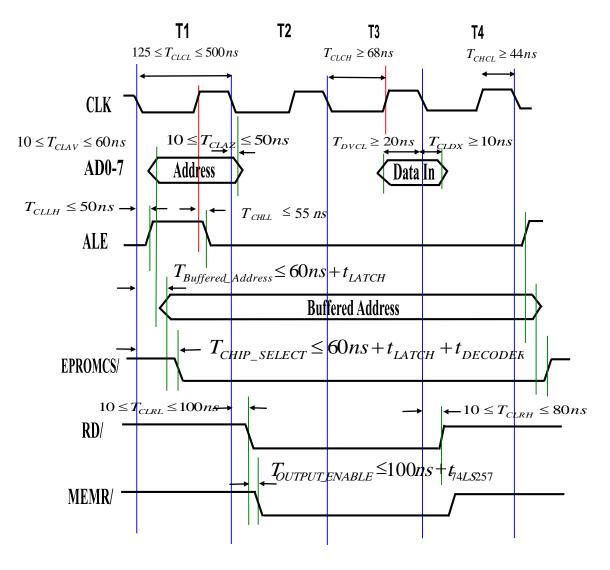

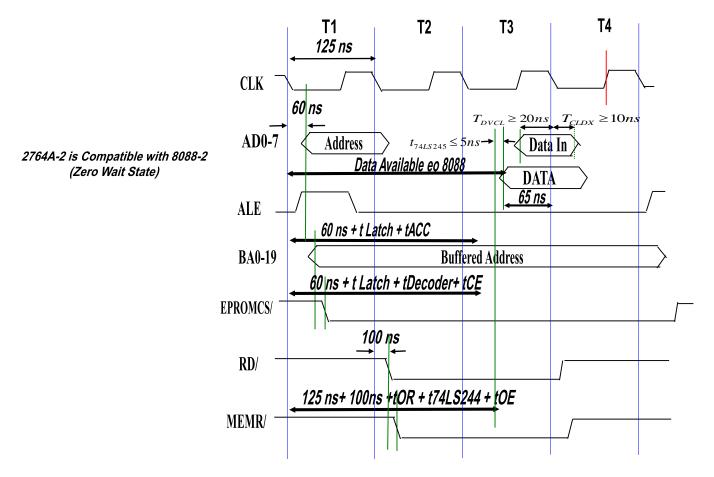

### **Example: Interfacing EPROM to 8088-2**

#### Mohammed Amer Arafah

### **Example: Interfacing EPROM to 8088-2**

CEN433 - King Saud University

#### Mohammed Amer Arafah

### **Example: Interfacing EPROM to 8088-2**

$EPROM\_OUTPUT = MAX\{60ns + t_{LATCH} + t_{ACC}, 60ns + t_{LATCH} + t_{Decoder} + t_{CE}, t_{T1} + 100ns + t_{OR} + t_{74LS244} + t_{OE}\}$

$Data_Avaiable_to_8088 = t_{74LS245} + MAX\{60ns + t_{LATCH} + t_{ACC}, 60ns + t_{LATCH} + t_{Decoder} + t_{CE}, t_{T1} + 100ns + t_{OR} + t_{74LS244} + t_{OE}\}$

## **RAM Memory Devices**

- Writing is needed more often than with EEPROMs → should be easier and faster.

- Two main types of RAM:

Static RAM

Dynamic RAM

# Static RAM (SRAM)

- A relatively complex cell circuit (several transistors per bit storage)

- That is why static RAM devices are more expensive and are typically smaller in capacity compared to dynamic RAM (A given # of transistors available on a chip gives fewer memory locations)

- Faster than dynamic RAMs, speeds down to 1 ns access time are now possible

- Used for high speed cache memories

- It is rarely the case that a large computer RAM uses only static memory type

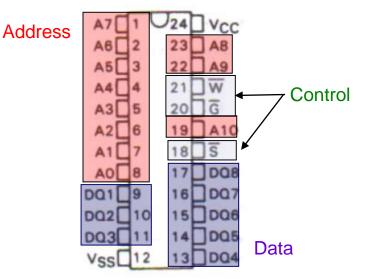

### **Static RAM Example: the 4016**

- 2K x 8 RAM (same size as the 2716)

- 11 bit address (A0-A10),

8-bit data (DQ1-DQ8): Data in/Data out

- Also produced with the numbers 2016, 4116, 6116, and 9028

- CS/ is S/, OE/ (RD/) is G/, WR/ is W/

- Range of speeds: access times in the range 120 ns to 250 ns (various chip versions, e.g. TMS4016-25 has 250 ns access time)

- All can be interfaced with the 8088/8086 without wait states

| PIN NOMENCLATURE |                  |  |  |  |  |

|------------------|------------------|--|--|--|--|

| A0 - A10         | Addresses        |  |  |  |  |

| DQ1 - DQ8        | Data In/Data Out |  |  |  |  |

| Ğ                | Output Enable    |  |  |  |  |

| S                | Chip Select      |  |  |  |  |

| Vcc              | + 5-V Supply     |  |  |  |  |

| VSS              | Ground           |  |  |  |  |

| W                | Write Enable     |  |  |  |  |

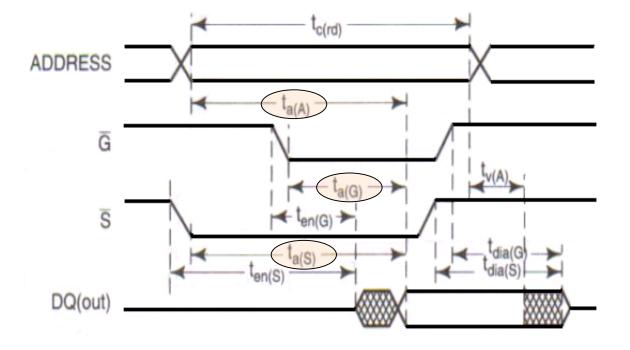

## **Static RAM Example: the 4016**

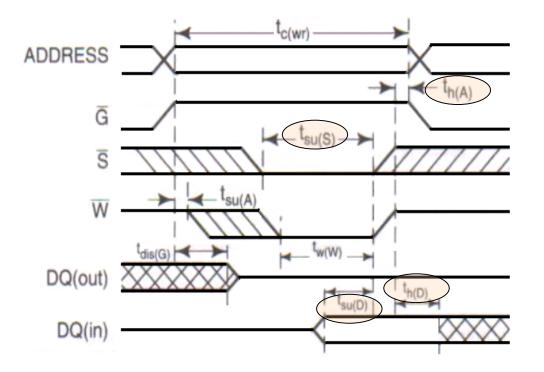

#### **Timing Waveform of Read Cycle**

## **Static RAM Example: the 4016**

#### **Timing Waveform of Write Cycle**

## Dynamic RAM (DRAM)

- Unlike static RAM, data is store as a voltage (charge) across a capacitor

- Charge of course leaks with time, and data needs to be refreshed (re-written) every say 2-4 ms

- Recent devices usually organized as XX K x 1 bit, largest 1G x 1

- Advantages:

- □ Simpler cell circuit

- □ Larger capacities

- While Largest SRAM  $\approx$  8 Mbits,

- Largest DRAM  $\approx$  1024 Mbits

- □ Lower cost than SRAM

- Disadvantages:

- □ Slower access times (e.g. 20 ns vs 1 ns)

- Select Storage

- □ Needs refreshing: e.g. every 4 ms max (added complexity)

#### But not that bad!:

Occurs during normal reads and writes. Also special hidden refresh cycles occurring simultaneously with other memory accesses (cycle stealing). Dedicated DRAM refresh controller chips available.

□ Large storage capacity  $\rightarrow$  large address inputs  $\rightarrow$  large number of chip pins required  $\rightarrow$  Need for chip pin multiplexing (added complexity)

CEN433 - King Saud University

Mohammed Amer Arafah

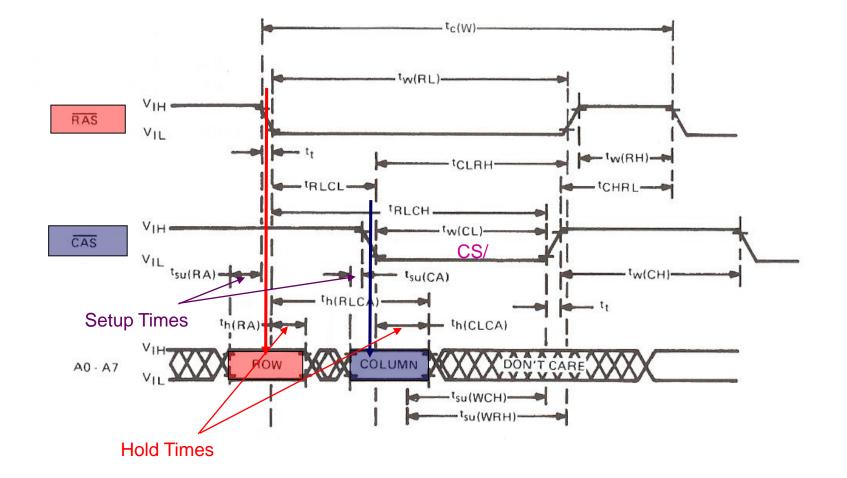

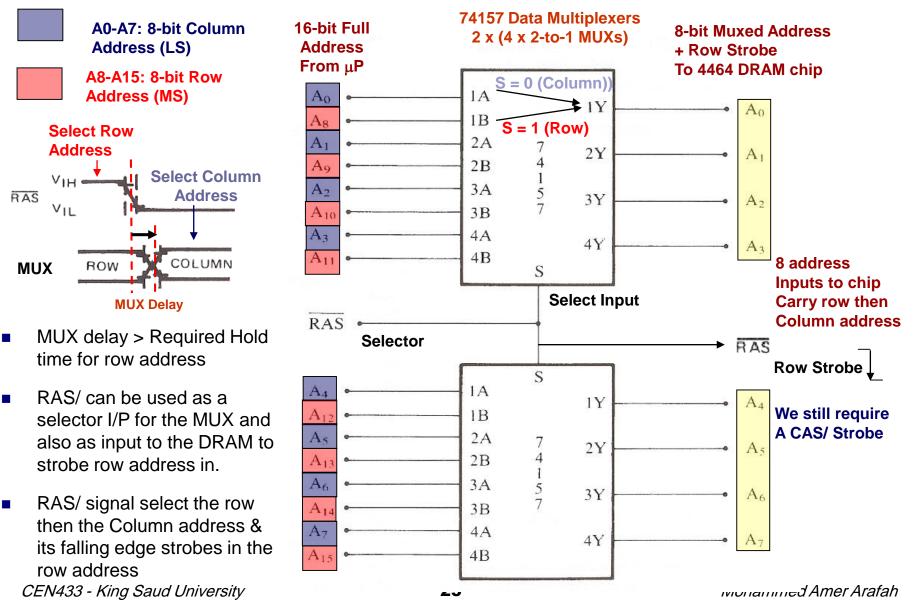

# **Dynamic RAM (DRAM)**

- 64 K x 4 DRAM

6 bits + 10 bits = 16 bits memory address

- But only 8 address lines on the chip!

- 16 address lines split into row and column 8-bit parts:

15987321016-bitRowColumn

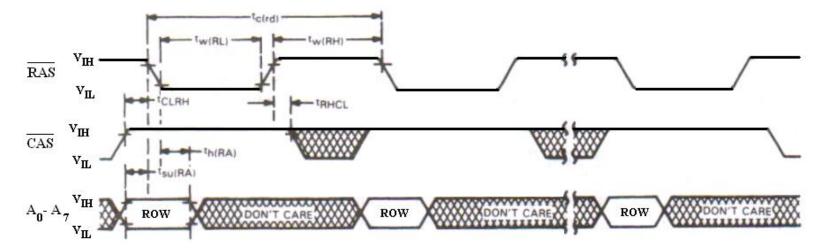

- Most significant 8-bit row address is first latched in using the RAS/ input (Row Address Select)

- Then 8-bit column address is latched in using the CAS/ input

- This loads the 16-bit address into a latch on the chip

- CAS/ also acts as CS/

- OE/ is G/, WE/ is W/, CS/ is CAS/

- Access time: Fastest version is 100 ns?

#### TI TMS4016 (64K ×4

| Pin(s)                           | Function              |

|----------------------------------|-----------------------|

| A <sub>0</sub> -A <sub>7</sub>   | Address               |

| DQ <sub>0</sub> -DQ <sub>3</sub> | Data In/Data Out      |

| RAS                              | Row Address Strobe    |

| CAS                              | Column Address Strobe |

| G                                | Output Enable         |

| W                                | Write Enable          |

### **Timing Diagram for Address Strobing**

CEN433 - King Saud University

### Multiplexing the Row/Column Address

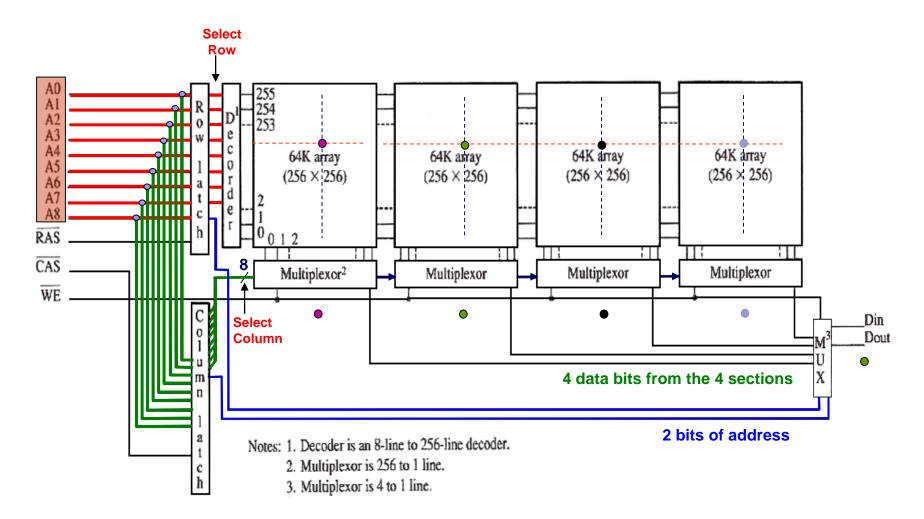

## **Internal Structure of a DRAM**

# **Internal Structure of a DRAM**

- 4 sections of 256 x 256 bits each

- Each section is addressed by 8 bits of rows and 8 bits for columns

- Remaining 2 address bits select the section addressed

- Row and column addresses are common to all 4 sections

- A whole row of 4 x 256 = 1024 bits is addressed simultaneously (Speeds up refreshing)

- The 4 data bits in the addressed column in the 4 sections are addressed simultaneously

- Only the bit from the required section is selected by the remaining 2 address bits using MUX3

## **DRAM Memory Refreshing**

- When a row is accessed in a refresh cycle, all memory cells on that row are refreshed

- This means that we need only 256 refresh operations to refresh all the 256K x 1 DRAM above

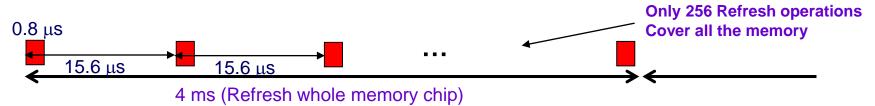

- To refresh the whole memory at the minimum rate of once every 4 ms, we need to do a refresh cycle every 4 ms/256 = 15.6 ms

- If a refresh cycle needs a bus cycle (4T with the 8088/86), the % of bus cycles lost for refreshing an 8088/86 running at a clock speed of 5 MHz is:

= 4 x 0.2 ms / 15.6 ms = 5.1% (not bad ... for the cost saving we achieve using dynamic RAM)

- For a Pentium 4 with a clock cycle of 3 GHz and a bus/instruction cycle of 1T, this % is:

= 1 x 0.33 ns / 15.6 ms = 0.2% (i.e. the penalty for DRAM refreshing is much more tolerable with modern, faster processors)

### **Refresh Cycle**

RAS/ only refresh cycles

#### The timing Diagram of the RAS/ refresh cycle for the TMS4464 DRAM

- RAS/ strobes a row address indicating the row of bits to be accessed for refreshing

- This row address is not a full memory address and can be generated by a small on-chip counter (e.g. 8-bits for the 256 rows in the 256K x 1 DRAM described)

- The row cells read are fed back for re-writing into the same locations to fulfill refresh requirements

# **Internal Structure of a DRAM**

#### EDO (Extended Data Output) Memory

- All 256 bits of the row from the selected section are saved in latches on the memory chip. So this data will be ready for future access without experiencing the slow memory access time again

- Such locations are close to the already accessed data, and are likely to be accessed soon (locality principle)

- □ Improves system performance by 15-25%

#### SDRAM (Synchronous Dynamic RAM) Memory

□ Memory runs synchronously to the system bus clock, e.g. at 100-133-200 MHz

#### Burst (block) Transfers

Burst transfers of say 4 x 64-bit numbers between the processor and the memory. First number experiences normal wait states, but 2<sup>nd</sup>, 3<sup>rd</sup>, and 4<sup>th</sup> transfers suffer no wait states, thus improving average access time.

#### DDR (Double Data Rate) Memory

- Data Transferred at double the SDRAM rate by using the two edges of the clock

- □ This does not exactly double the data transfer rate due to access time limitations

#### Combinations exist, e.g. DDR SDRAM

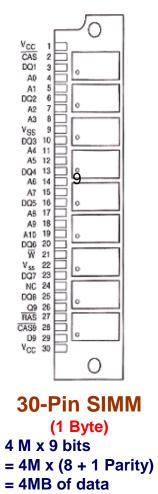

# **DRAM Memory Modules**

- DRAMs are often mounted on memory modules interfaced to the PC

- SIMM: Single In-Line Memory Module: Devices and connection pins mounted on one side. Available in 2 types:

- Older 30-Pin SIMMs

- Newer 72-Pin SIMMs

- DIMM: Dual In-Line Memory Module: Devices and pins mounted on both sides. 168-Pin

Used for Pentium- Pentium 4 processors with 64-bit data bus (8 Bytes of data for each memory address)

Card can have one EPROM containing info on size and speed of the devices for Plugand-Play use

#### 72-Pin SIMM (4 Bytes)

#### 4 M x 36 bits = 4M x (32 + 4 Parity) = 16 MB of data

Larger address

Wider data bus

**168-Pin DIMM** (8 Bytes) 4 M x 64 bits = 32 MB of data In DRAM, EDO, and

SDRAM