# William Stallings Data and Computer Communications

#### Chapter 6 Digital Data Communications Techniques

# **Digital Data Communications Techniques**

# **Synchronization**

#### **American Standards Committee for Information Interchange (ASCII):**

|   | D:4     |    | 7 | 0   | 0   | 0  | 0  | 1 | 1 | 1 | 1   |

|---|---------|----|---|-----|-----|----|----|---|---|---|-----|

| _ | Bit     |    | 6 | 0   | 0   | 1  | 1  | 0 | 0 | 1 | 1   |

| P | osition | IS | 5 | 0   | 1   | 0  | 1  | 0 | 1 | 0 | 1   |

| 4 | 3       | 2  | 1 |     |     |    |    |   |   |   |     |

| 0 | 0       | 0  | 0 | NUL | DLE | SP | 0  | @ | P | \ | р   |

| 0 | 0       | 0  | 1 | SOH | DC1 | !  | 1  | Α | Q | a | q   |

| 0 | 0       | 1  | 0 | STX | DC2 | 66 | 2  | B | R | b | r   |

| 0 | 0       | 1  | 1 | ETX | DC3 | #  | 3  | С | S | c | S   |

| 0 | 1       | 0  | 0 | EOT | DC4 | \$ | 4  | D | Т | d | t   |

| 0 | 1       | 0  | 1 | ENQ | NAK | %  | 5  | E | U | e | u   |

| 0 | 1       | 1  | 0 | ACK | SYN | &  | 6  | F | V | f | V   |

| 0 | 1       | 1  | 1 | BEL | ETB | ,  | 7  | G | W | g | W   |

| 1 | 0       | 0  | 0 | BS  | CAN | (  | 8  | H | X | h | X   |

| 1 | 0       | 0  | 1 | HT  | EM  | )  | 9  | Ι | Y | i | У   |

| 1 | 0       | 1  | 0 | LF  | SUB | *  | •• | J | Z | j | Z   |

| 1 | 0       | 1  | 1 | VT  | ESC | +  | ;  | K | [ | k | {   |

| 1 | 1       | 0  | 0 | FF  | FS  | ,  | <  | L | \ | 1 |     |

| 1 | 1       | 0  | 1 | CR  | GS  | -  | I  | Μ | ] | m | }   |

| 1 | 1       | 1  | 0 | SO  | RS  | •  | >  | Ν | ^ | n | ~   |

| 1 | 1       | 1  | 1 | SI  | US  | /  | ?  | 0 |   | 0 | DEL |

#### **American Standards Committee for Information Interchange (ASCII):**

|     | <b>D</b> !/ |   | 7 | 0   | 0   | 0  | 0 | 1 | 1   | 1 | 1   |

|-----|-------------|---|---|-----|-----|----|---|---|-----|---|-----|

| Bit |             |   | 6 | 0   | 0   | 1  | 1 | 0 | 0   | 1 | 1   |

| P   | Positions   |   |   | 0   | 1   | 0  | 1 | 0 | 1   | 0 | 1   |

| 4   | 3           | 2 | 1 |     |     | -  |   | - |     |   |     |

| 0   | 0           | 0 | 0 | NUL | DLE | SP | 0 | @ | Р   | \ | р   |

| 0   | 0           | 0 | 1 | SOH | DC1 | !  | 1 | Α | Q   | a | q   |

| 0   | 0           | 1 | 0 | STX | DC2 | 66 | 2 | В | R   | b | r   |

| 0   | 0           | 1 | 1 | ETX | DC3 | #  | 3 | С | S   | c | S   |

| 0   | 1           | 0 | 0 | EOT | DC4 | \$ | 4 | D | Т   | d | t   |

| 0   | 1           | 0 | 1 | ENQ | NAK | %  | 5 | Ε | U   | e | u   |

| 0   | 1           | 1 | 0 | ACK | SYN | &  | 6 | F | V   | f | v   |

| 0   | 1           | 1 | 1 | BEL | ETB | ,  | 7 | G | W   | g | w   |

| 1   | 0           | 0 | 0 | BS  | CAN | (  | 8 | Η | X   | h | X   |

| 1   | 0           | 0 | 1 | HT  | EM  | )  | 9 | Ι | Y   | i | У   |

| 1   | 0           | 1 | 0 | LF  | SUB | *  | : | J | Z   | j | Z   |

| 1   | 0           | 1 | 1 | VT  | ESC | +  | ; | K | ] [ | k | {   |

| 1   | 1           | 0 | 0 | FF  | FS  | ,  | < | L |     | l |     |

| 1   | 1           | 0 | 1 | CR  | GS  | -  | = | Μ | ]   | m | }   |

| 1   | 1           | 1 | 0 | SO  | RS  | •  | > | Ν | ^   | n | ~   |

| 1   | 1           | 1 | 1 | SI  | US  | /  | ? | 0 |     | 0 | DEL |

#### **Extended Binary Coded Decimal Interchange Code (EBCDIC):**

|     |           |   | 8 | 0   | 0   | 0   | 0   | 0  | 0  | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

|-----|-----------|---|---|-----|-----|-----|-----|----|----|---|---|---|---|---|---|---|---|---|---|

| Bit |           |   | 7 | 0   | 0   | 0   | 0   | 1  | 1  | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| P   | Positions |   | 6 | 0   | 0   | 1   | 1   | 0  | 0  | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

|     |           |   | 5 | 0   | 1   | 0   | 1   | 0  | 1  | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

| 4   | 4 3 2     |   | 1 |     |     |     |     |    |    |   |   |   |   |   |   |   |   |   |   |

| 0   | 0         | 0 | 0 | NUL | DLE | DS  |     | SP | &  | - |   |   |   |   |   |   |   |   | 0 |

| 0   | 0         | 0 | 1 | SOH | DC1 | SOS |     |    |    | / |   | a | j |   |   | Α | J |   | 1 |

| 0   | 0         | 1 | 0 | STX | DC2 | FS  | SYN |    |    |   |   | b | k | S |   | B | K | S | 2 |

| 0   | 0         | 1 | 1 | ETX | DC3 |     |     |    |    |   |   | c | l | t |   | С | L | Т | 3 |

| 0   | 1         | 0 | 0 | PF  | RES | BYP | PN  |    |    |   |   | d | m | u |   | D | Μ | U | 4 |

| 0   | 1         | 0 | 1 | HT  | NL  | LF  | RS  |    |    |   |   | e | n | v |   | E | Ν | V | 5 |

| 0   | 1         | 1 | 0 | LC  | BS  | EOB | UC  |    |    |   |   | f | 0 | W |   | F | 0 | W | 6 |

| 0   | 1         | 1 | 1 | DEL | IL  | PRE | EOT |    |    |   |   | g | р | X |   | G | Р | Χ | 7 |

| 1   | 0         | 0 | 0 |     | CAN |     |     |    |    |   |   | h | q | у |   | Η | Q | Y | 8 |

| 1   | 0         | 0 | 1 |     | EM  |     |     |    |    |   |   | i | r | Z |   | Ι | Ν | Ζ | 9 |

| 1   | 0         | 1 | 0 | SMM | CC  | SM  |     | ¢  | !  |   | : |   |   |   |   |   |   |   |   |

| 1   | 0         | 1 | 1 | VT  |     |     |     | •  | \$ | , | # |   |   |   |   |   |   |   |   |

| 1   | 1         | 0 | 0 | FF  | IFS |     | DC4 | <  | *  | % | @ |   |   |   |   |   |   |   |   |

| 1   | 1         | 0 | 1 | CR  | IGS | ENQ | NAK | (  | )  | - | , |   |   |   |   |   |   |   |   |

| 1   | 1         | 1 | 0 | SO  | IRS | ACK |     | +  | ;  | > | = |   |   |   |   |   |   |   |   |

| 1   | 1         | 1 | 1 | SI  | IUS | BEL | SUB |    | 7  | ? | " |   |   |   |   |   |   |   |   |

#### **Extended Binary Coded Decimal Interchange Code (EBCDIC):**

|     |           |   | 8 | 0   | 0   | 0   | 0   | 0  | 0  | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

|-----|-----------|---|---|-----|-----|-----|-----|----|----|---|---|---|---|---|---|---|---|---|---|

| Bit |           |   | 7 | 0   | 0   | 0   | 0   | 1  | 1  | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| P   | Positions |   | 6 | 0   | 0   | 1   | 1   | 0  | 0  | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

|     |           |   | 5 | 0   | 1   | 0   | 1   | 0  | 1  | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

| 4   | 4 3 2     |   | 1 |     |     |     |     |    |    |   |   |   |   |   |   |   |   |   |   |

| 0   | 0         | 0 | 0 | NUL | DLE | DS  |     | SP | &  | - |   |   |   |   |   |   |   |   | 0 |

| 0   | 0         | 0 | 1 | SOH | DC1 | SOS |     |    |    | / |   | a | j |   |   | Α | J |   | 1 |

| 0   | 0         | 1 | 0 | STX | DC2 | FS  | SYN |    |    |   |   | b | k | S |   | B | K | S | 2 |

| 0   | 0         | 1 | 1 | ETX | DC3 |     |     |    |    |   |   | c | l | t |   | C | L | Т | 3 |

| 0   | 1         | 0 | 0 | PF  | RES | BYP | PN  |    |    |   |   | d | m | u |   | D | Μ | U | 4 |

| 0   | 1         | 0 | 1 | HT  | NL  | LF  | RS  |    |    |   |   | e | n | v |   | E | Ν | V | 5 |

| 0   | 1         | 1 | 0 | LC  | BS  | EOB | UC  |    |    |   |   | f | 0 | w |   | F | 0 | W | 6 |

| 0   | 1         | 1 | 1 | DEL | IL  | PRE | EOT |    |    |   |   | g | р | X |   | G | Р | Χ | 7 |

| 1   | 0         | 0 | 0 |     | CAN |     |     |    |    |   |   | h | q | у |   | H | Q | Y | 8 |

| 1   | 0         | 0 | 1 |     | EM  |     |     |    |    |   |   | i | r | Z |   | Ι | Ν | Ζ | 9 |

| 1   | 0         | 1 | 0 | SMM | CC  | SM  |     | ¢  | !  |   | : |   |   |   |   |   |   |   |   |

| 1   | 0         | 1 | 1 | VT  |     |     |     | •  | \$ | , | # |   |   |   |   |   |   |   |   |

| 1   | 1         | 0 | 0 | FF  | IFS |     | DC4 | <  | *  | % | @ |   |   |   |   |   |   |   |   |

| 1   | 1         | 0 | 1 | CR  | IGS | ENQ | NAK | (  | )  | - | , |   |   |   |   |   |   |   |   |

| 1   | 1         | 1 | 0 | SO  | IRS | ACK |     | +  | ;  | > | = |   |   |   |   |   |   |   |   |

| 1   | 1         | 1 | 1 | SI  | IUS | BEL | SUB |    | 7  | ? | " |   |   |   |   |   |   |   |   |

# **Synchronization**

**#**To correctly interpret the signals received, the **receiver's bit intervals must correspond exactly to the sender's bit intervals** (the same clock rate).

#timing problems require a mechanism to synchronize the transmitter and receiver

In the transmitter and receiver

In the transmitter and drifting will sample at wrong time after sufficient bits are sent

## **Lack of Synchronization**

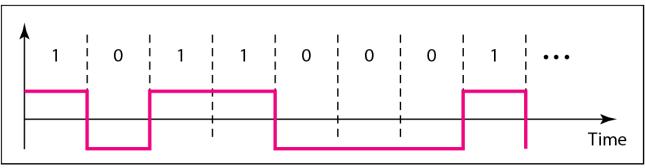

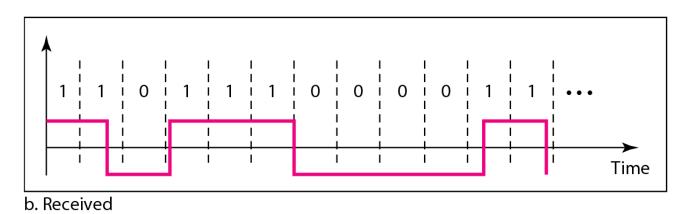

#### **#Example:** Faster receiver clock

a. Sent

## **Synchronization**

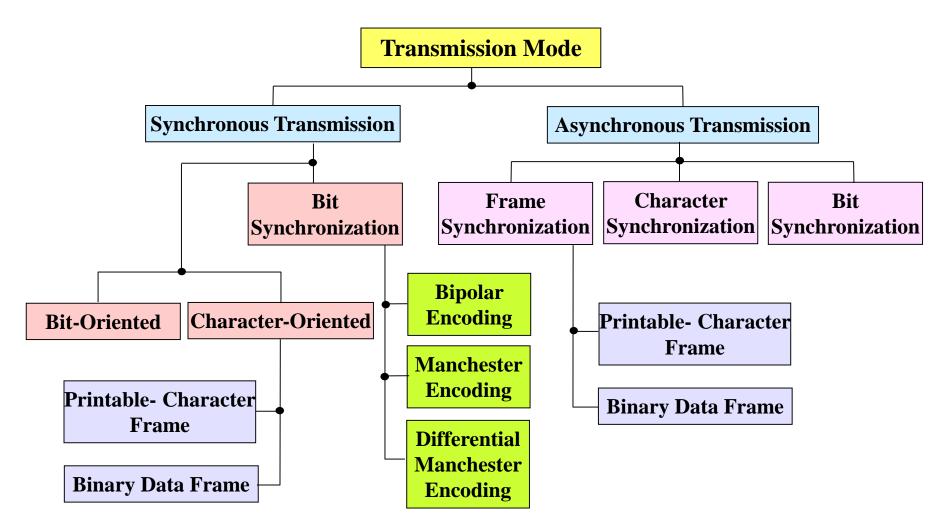

**#**Two solutions to synchronizing clocks

△Asynchronous transmission

**Synchronous transmission**

#### **Transmission Modes**

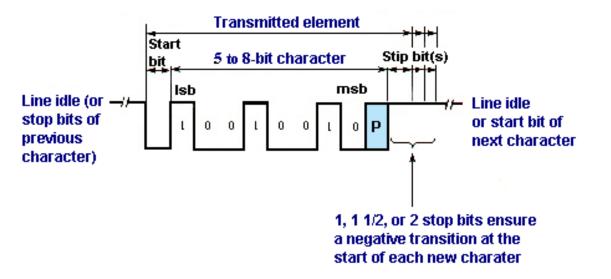

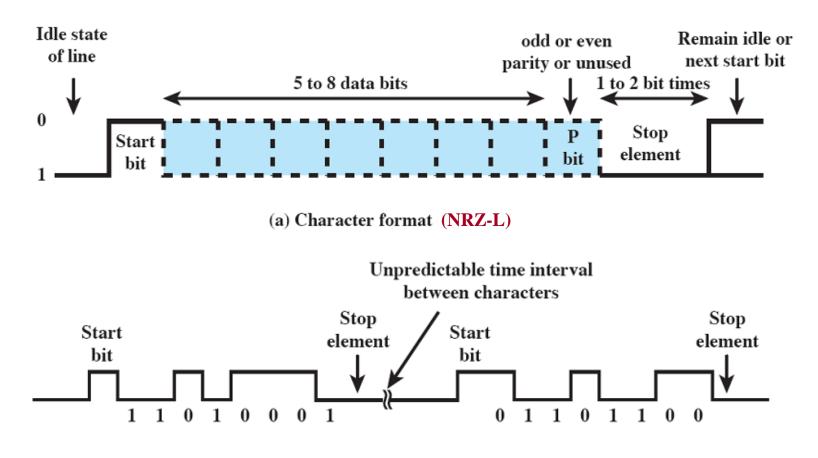

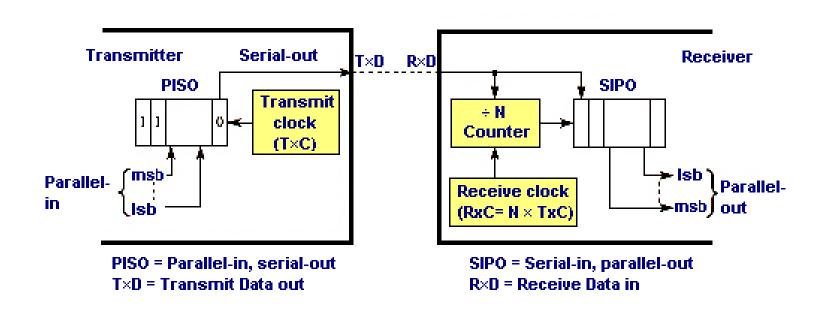

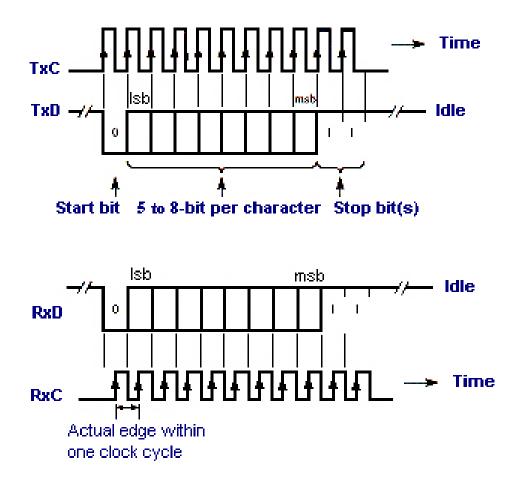

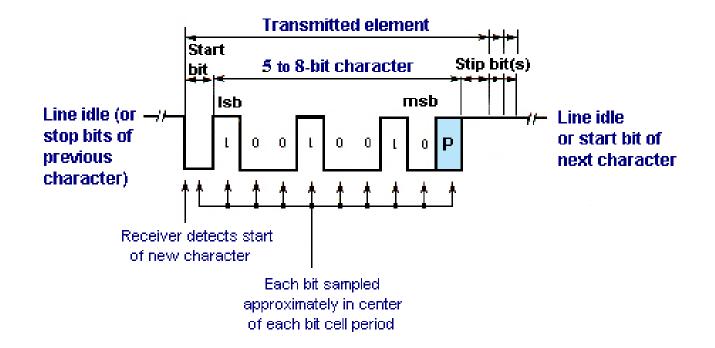

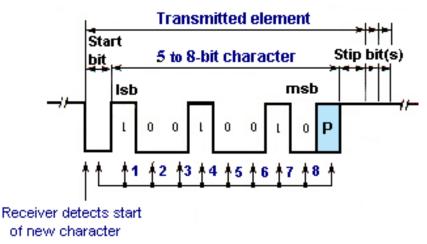

- **In asynchronous transmission**, the receiver clock (R×C) runs unsynchronized with respect to the incoming signal (R×D).

- Each character (byte) is encapsulated between an additional start bit and one or more stop bits.

- ₭ The state of the signal on the transmission line between characters is idle state.

Send one character (e.g. 8 bits) at a time **#** no data: idle state (usually negative volt) **#**start bit (usually zero) **# data:** usually use NRZ-L **# party bit** can be added for error control **# stop bit**, 1-2 bit time, same as idle  $\mathbb{H}$ timing requirement is modest (within 1 char)

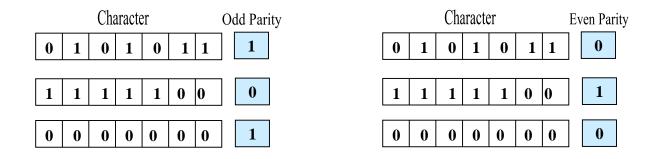

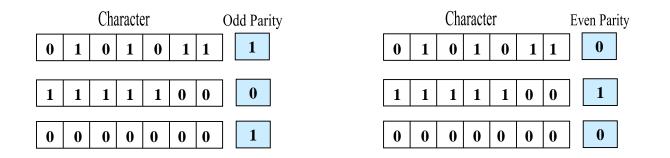

#### **# Parity**

parity bit set so character has even (even parity) or odd (odd parity) number of ones

Error Detection

(b) 8-bit asynchronous character stream (NRZ-L)

William Stallings "Data and Computer Communications"

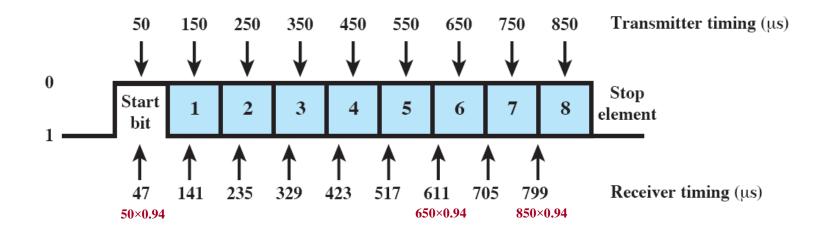

Bata rate = 10 kbps, bit time = 0.1 ms = 100 µs

Receiver is faster by 6% of bit time = 6 µs

Receiver samples bit every 94 µs

Last bit is in error

In previous example, actually two errors

□ last bit is incorrect

○ When a valid stop bit is not detected at end of each character (i.e., it is supposed to be logic 1 and found logic 0) → Framing Error

Disadvantage

A requires overhead 2 to 4 bits / character

In for 8 bit char, no parity, 1 stop bit, 20% overhead

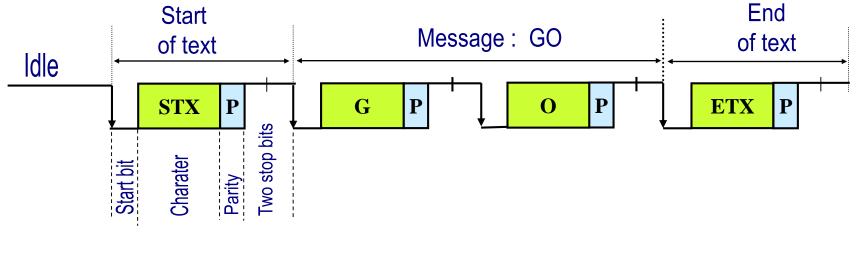

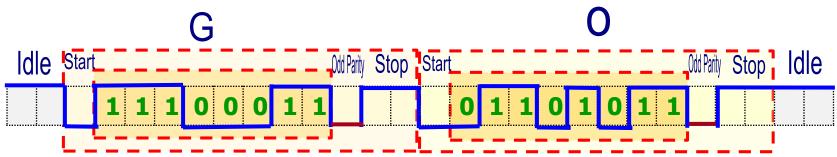

Construct the transmitted frame using **asynchronous transmission mode** which contains the following data: **GO**. Assume that the number of bits per character is 8, the number of stop bits is 2, and parity bit is used.

Efficiency ( $\eta$ )= 8/(1+8+1+2) = 8/12 = 66.67%

Construct the transmitted frame using **asynchronous transmission mode** which contains the following data: **GO**. Assume that the number of bits per character is 8, the number of stop bits is 2, and odd parity bit is used.

#### Hints:

- 1. No need to include framing characters such as STX and ETX

- 2. G=1100 0111, O=1101 0110, STX=1101 0110, ETX=1101 0110

- 3. The least significant bit (**Isb**) is transmitted first

Efficiency ( $\eta$ )= 8/(1+8+1+2) = 8/12 = 66.67%

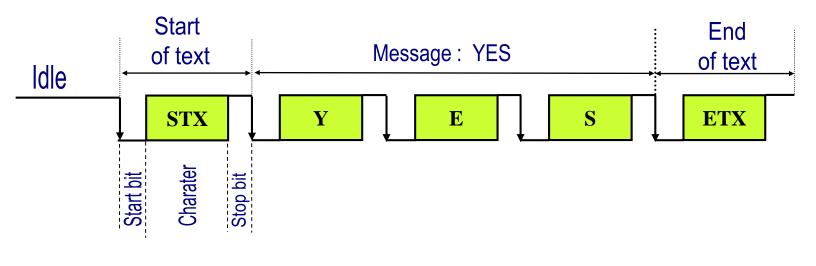

Construct the transmitted frame using **asynchronous transmission mode** which contains the following data: **YES**. Assume that the number of bits per character is 7, the number of stop bits is 1 and no parity bit is used.

Efficiency  $(\eta) = 7/(1+7+1) = 7/9 = 77.78\%$

Construct the transmitted frame using **asynchronous transmission mode** which contains the following data: **YES**. Assume that the number of bits per character is 7, the number of stop bits is 1 and no parity bit is used.

#### Hints:

- 1. No need to include framing characters such as STX and ETX

- 2. Y=101 1001, E=100 0101, S=101 0011

- 3. The least significant bit (lsb) is transmitted first

Efficiency  $(\eta) = 7/(1+7+1) = 7/9 = 77.78\%$

#### **Bit Synchronization using Asynchronous Transmission:**

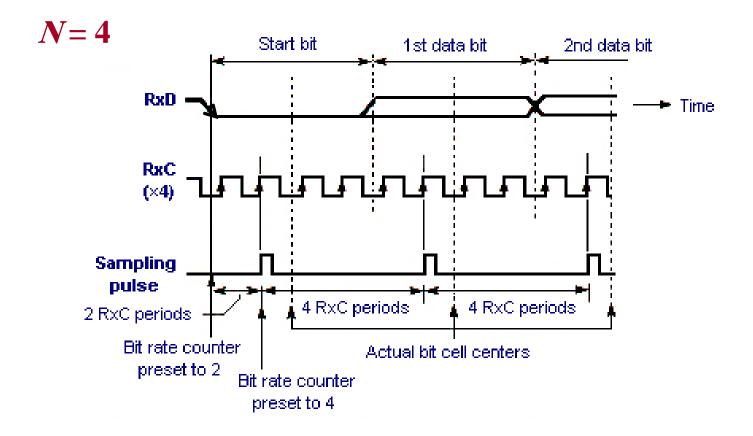

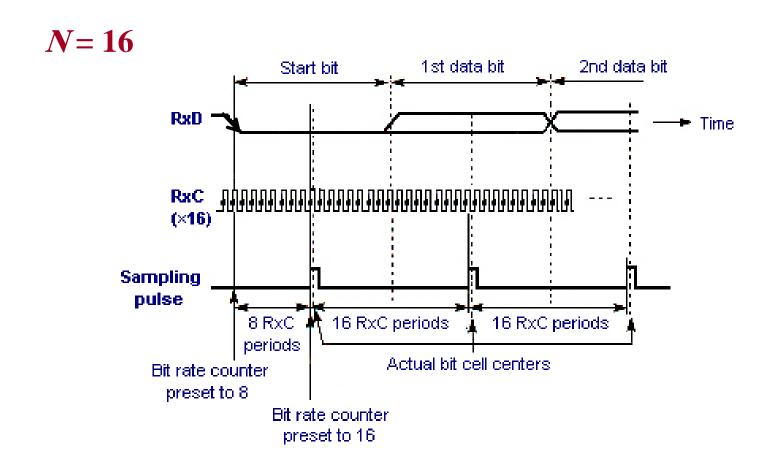

- **#** The first  $1 \rightarrow 0$  transition is associated with the start bit.

- **# Each bit is sampled at the center to avoid delay distortion** problem.

- **\*** After the first transition is detected, the signal is sampled after *N*/2 clock cycles and then subsequently after *N* clock cycles for each bit in the character.

#### **Character Synchronization using Asynchronous Transmission:**

After the start bit is detected, the receiver achieves character synchronization simply **by counting the programmed number of bits.**

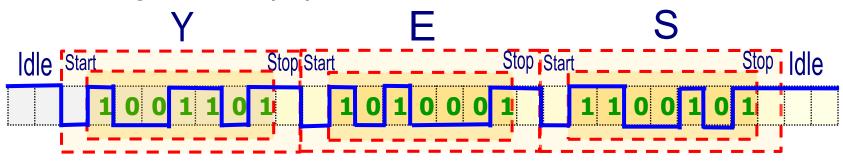

#### Frame Synchronization using Asynchronous Transmission:

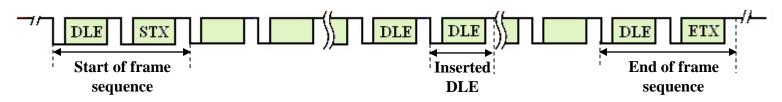

- ₭ Frame synchronization is used to determine the start and end of frame.

- **#** 1. Printable Characters

- Encapsulate the complete block between two non-printable characters: STX (start-of-text) and ETX (end-of-text).

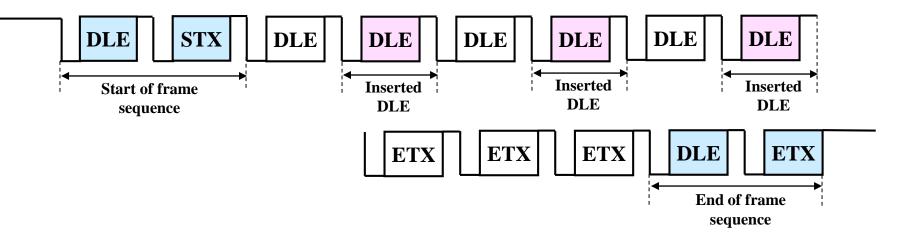

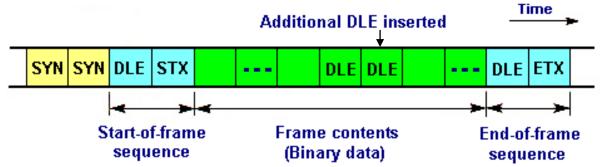

#### **#** 2. Binary Data

Construct the transmitted frame using asynchronous transmission mode which contains the following binary data: **DLE DLE DLE ETX ETX ETX.** Assume that the number of stop bits is 1 and no parity bit is used.

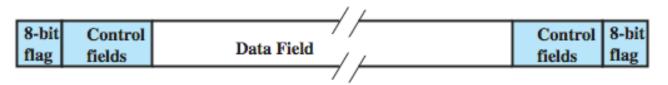

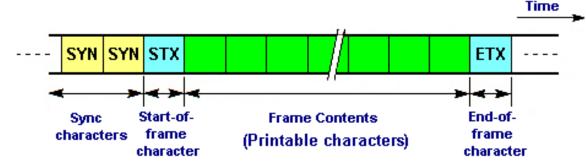

**#** block of data transmitted sent as a frame

#### **%** No start or stop bits

#### **# clocks must be synchronized**

can use separate clock line

or embed clock signal in data

#### **#** need to indicate start and end of block

☐ use preamble and postamble

#### **# more efficient** (lower overhead) than async

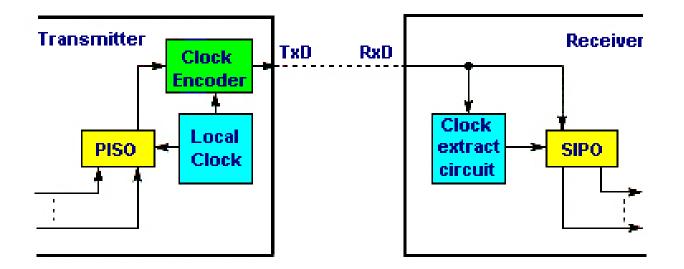

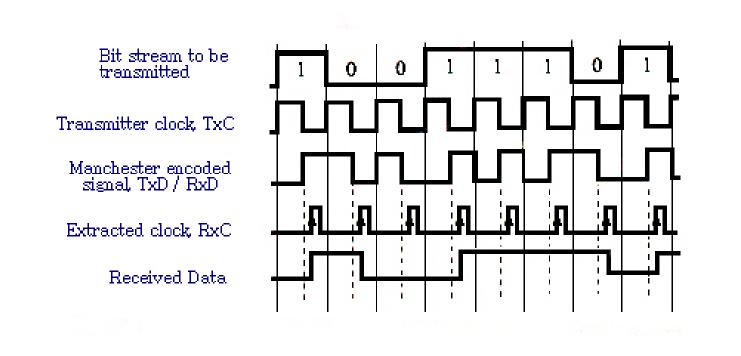

#### **Clock Encoding and Extraction**:

#### **Clock Encoding and Extraction:**

#### **Character-Oriented Synchronous Transmission:**

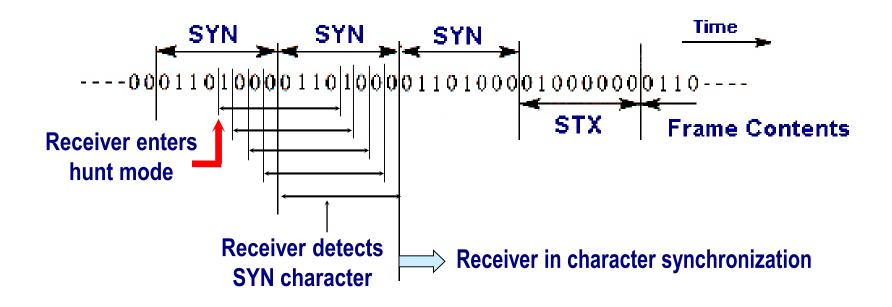

- ℜ Once the receiver has obtained bit synchronization, it enters Hunt Mode.

- When the receiver enters hunt mode, it starts to interpret the received bit stream in a window of 8 bits as each new bit is received. It checks whether the last eight bits were equal to SYN character. If they are not, it receives the next bit and repeats the check. If they are, then the correct character boundary is found and hence the following characters are then read after each subsequent eight bits have been received.

#### **Character-Oriented Synchronous Transmission:**

#### **Character-Oriented Synchronous Transmission:**

#### **1. Printable characters:**

#### 2. Binary data:

# **Digital Data Communications Techniques**

# **Error Detection & Correction**

# **Types of Error**

# an error occurs when a bit is altered between transmission and reception

#### **% Single bit errors**

□ caused by white noise

#### **# Burst errors**

contiguous sequence of *B* bits in which first and last and any number of intermediate bits in error

caused by impulse noise or by fading in wireless

effect greater at higher data rates

#### **Error Detection**

# **Error Detection**

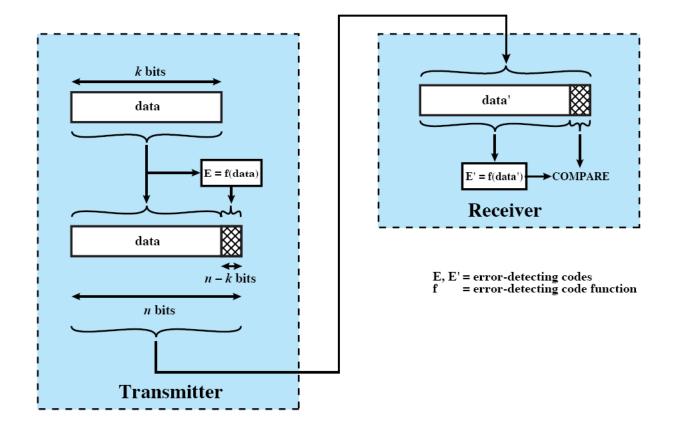

#### **Error Detection Process**

## **Error Detection**

#### **# Parity**

parity bit set so character has even (even parity) or odd (odd parity) number of ones

even number of bit errors goes undetected

# **Cyclic Redundancy Check**

**#**one of **most common** and **powerful checks**

#for block of k bits transmitter generates an n bit

frame check sequence (FCS)

# **#transmits** *k+n* bits which is exactly divisible by some number

% receiver divides frame by that number

△if no remainder, assume no error

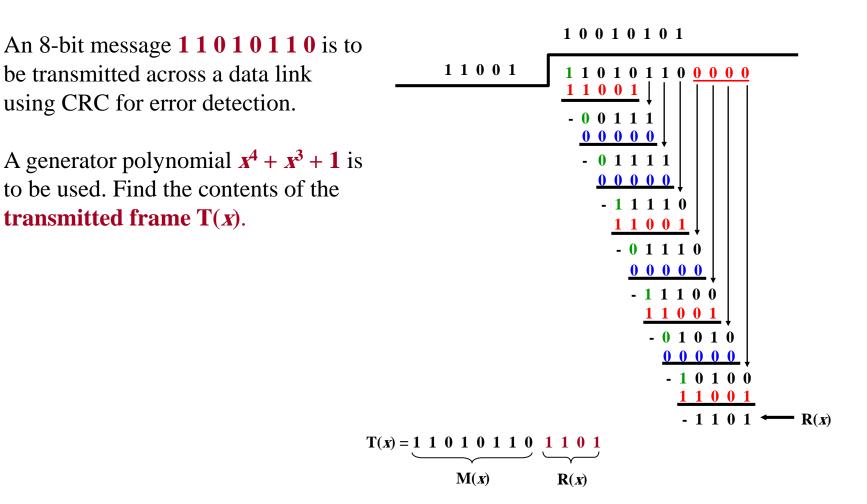

## Cyclic Redundancy Check Example 1

William Stallings "Data and Computer Communications"

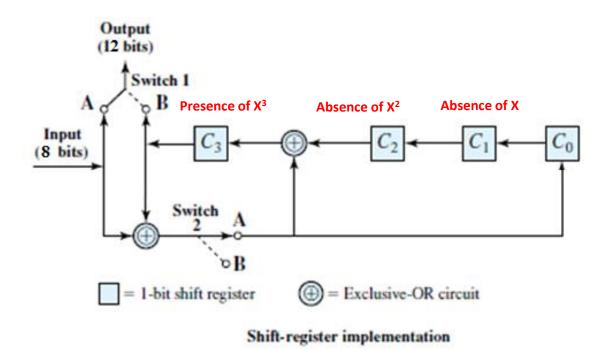

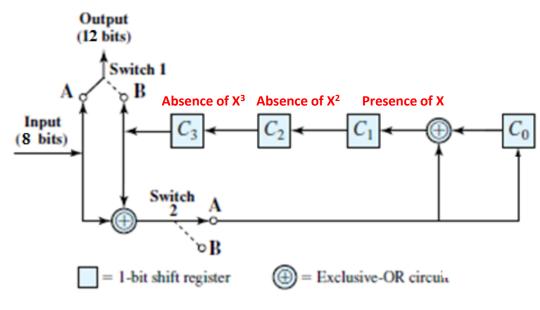

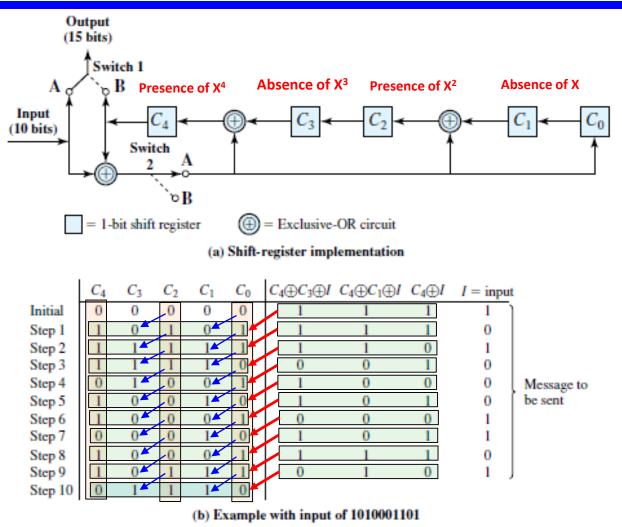

## Cyclic Redundancy Check Example 1 – Circuit Implementation

#### Generator Polynomial $x^4 + x^3 + 1$

The circuit is implemented as follows:

- 1. The register contains n k bits, equal to the length of the FCS.

- 2. There are up to n k XOR gates.

- The presence or absence of a gate corresponds to the presence or absence of a term in the divisor polynomial, P(X), excluding the terms 1 and X<sup>n-k</sup>.

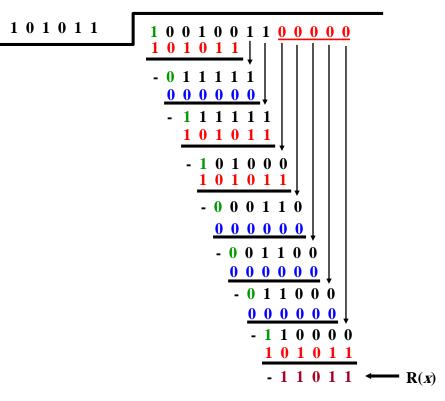

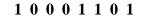

## Cyclic Redundancy Check Example 2

An 8-bit message **10010011** is to be transmitted across a data link using CRC for error detection.

A generator polynomial  $x^5 + x^3 + x + 1$ is to be used. Find the contents of the **transmitted frame** T(x). 1 0 1 1 0 0 0 1

$$T(x) = \underbrace{1 \ 0 \ 0 \ 1 \ 0 \ 0 \ 1 \ 1}_{M(x)} \underbrace{1 \ 1 \ 0 \ 1 \ 1}_{R(x)}$$

William Stallings "Data and Computer Communications"

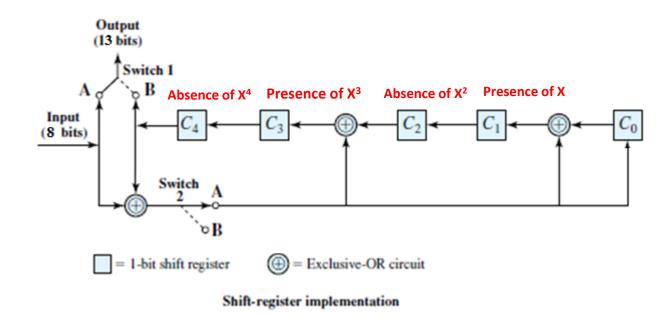

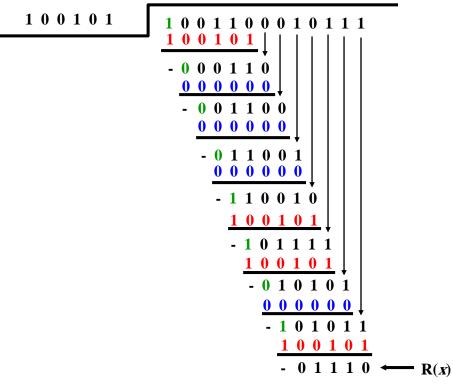

## Cyclic Redundancy Check Example 2 – Circuit Implementation

#### Generator Polynomial $x^5 + x^3 + x + 1$

The circuit is implemented as follows:

- 1. The register contains n k bits, equal to the length of the FCS.

- 2. There are up to n k XOR gates.

- The presence or absence of a gate corresponds to the presence or absence of a term in the divisor polynomial, P(X), excluding the terms 1 and X<sup>n-k</sup>.

## **Cyclic Redundancy Check Example 3**

#### Assume that the following frame: 111101101100is received across a data link using CRC for error detection. A generator polynomial $x^4 + x + 1$ is to be used. Check whether the received frame is correct or incorrect. If the frame is correct, then deduce the original message.

1 1 1 0 0 1 0 0

$\mathbf{R}(\mathbf{x}) = \mathbf{0} \rightarrow$  The Message is correct

$\rightarrow$  M(x) = 1 1 1 1 0 1 1 0

## Cyclic Redundancy Check Example 3 – Circuit Implementation

#### Generator Polynomial $x^4 + x + 1$

The circuit is implemented as follows:

- 1. The register contains n k bits, equal to the length of the FCS.

- 2. There are up to n k XOR gates.

- The presence or absence of a gate corresponds to the presence or absence of a term in the divisor polynomial, P(X), excluding the terms 1 and X<sup>n-k</sup>.

Shift-register implementation

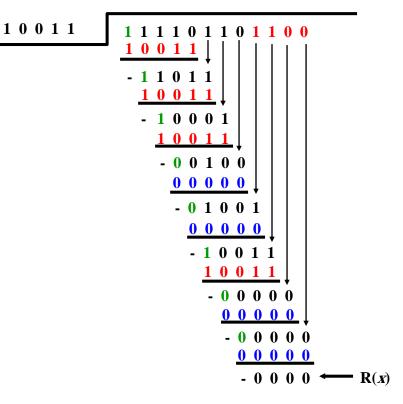

## Cyclic Redundancy Check Example 4

Assume that the following frame:

1001100010111 is **received** across a data link using CRC for error detection. A generator polynomial  $x^5 + x^2 + 1$  is to be used. Check whether the received frame is correct or incorrect. If the frame is correct, then deduce the original

message.

→ Error is detected.

→ The message is discarded.

## Cyclic Redundancy Check Example 4 – Circuit Implementation

#### Generator Polynomial $x^5 + x^2 + 1$

The circuit is implemented as follows:

- 1. The register contains n k bits, equal to the length of the FCS.

- 2. There are up to n k XOR gates.

- The presence or absence of a gate corresponds to the presence or absence of a term in the divisor polynomial, P(X), excluding the terms 1 and X<sup>n-k</sup>.

Shift-register implementation

#### **Cyclic Redundancy Check**

- **#** Four versions of **Polynomial Division** P(X) are widely used:

- $\text{CRC-12} = X^{12} + X^{11} + X^3 + X^2 + X + 1$

- **#** CRC-16 =  $X^{16} + X^{15} + X^2 + 1$

- **#** CRC-CCITT =  $X^{16} + X^{12} + X^5 + 1$

- $\begin{array}{l} \mbox{$\texttt{K}$ CRC-32 = X^{32} + X^{26} + X^{23} + X^{22} + X^{16} + X^{12} + X^{11} + X^{10} + X^8 + X^7 + X^5$} \\ & + X^4 + X^2 + X + 1 \end{array}$

- **# CRC-32 is used in IEEE 802 LAN standards.**

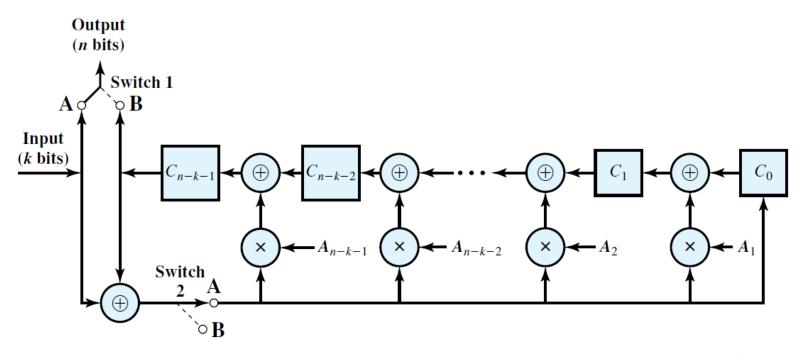

## **Cyclic Redundancy Check Implementation**

- H The entire register is clocked simultaneously, causing a 1-bit shift along the entire register. The circuit is implemented as follows:

- 1. The register contains *n*-*k* bits, equal to the length of the FCS.

- 2. There are up to *n-k* XOR gates.

- 3. The presence or absence of a gate corresponds to the presence or absence of a term in the divisor polynomial, P(X), excluding the *terms 1 and X*<sup>*n-k*</sup>.

#### **Cyclic Redundancy Check Implementation**

**EXAMPLE 6.8** The architecture of a CRC circuit is best explained by first considering an example, which is illustrated in Figure 6.5. In this example, we use

| Data $D = 1010001101;$ | $D(X) = X^9 + X^7 + X^3 + X^2 + 1$ |

|------------------------|------------------------------------|

| Divisor $P = 110101;$  | $P(X) = X^5 + X^4 + X^2 + 1$       |

which were used earlier in the discussion.

Figure 6.5a shows the shift register implementation. The process begins with the shift register cleared (all zeros). The message, or dividend, is then entered, one bit at a time, starting with the most significant bit. Figure 6.5b is a table that shows the step-by-step operation as the input is applied one bit at a time. Each row of the table shows the values currently stored in the five shift-register elements. In addition, the row shows the values that appear at the outputs of the three XOR circuits. Finally, the row shows the value of the next input bit, which is available for the operation of the next step.

Note that the XOR operation affects  $C_4$ ,  $C_2$ , and  $C_0$  on the next shift. This is identical to the binary long division process illustrated earlier. The process continues through all the bits of the message. To produce the proper output, two switches are used. The input data bits are fed in with both switches in the A position. As a result, for the first 10 steps, the input bits are fed into the shift register and also used as output bits. After the last data bit is processed, the shift register contains the remainder (FCS) (shown shaded). As soon as the last data bit is provided to the shift register, both switches are set to the B position. This has two effects: (1) All of the XOR gates become simple pass-throughs; no bits are changed, and (2) as the shifting process continues, the 5 CRC bits are output.

At the receiver, the same logic is used. As each bit of M arrives, it is inserted into the shift register. If there have been no errors, the shift register should contain the bit pattern for R at the conclusion of M. The transmitted bits of R now begin to arrive, and the effect is to zero out the register so that, at the conclusion of reception, the register contains all 0s.

William Stallings "Data and Computer Communications"

# Circuit with Shift Registers for Dividing by the Polynomial $X^5 + X^4 + X^2 + 1$

# Circuit with Shift Registers for Dividing by the Polynomial $X^5 + X^4 + X^2 + 1$

Dr. Mohammed Arafah

William Stallings "Data and Computer Communications"

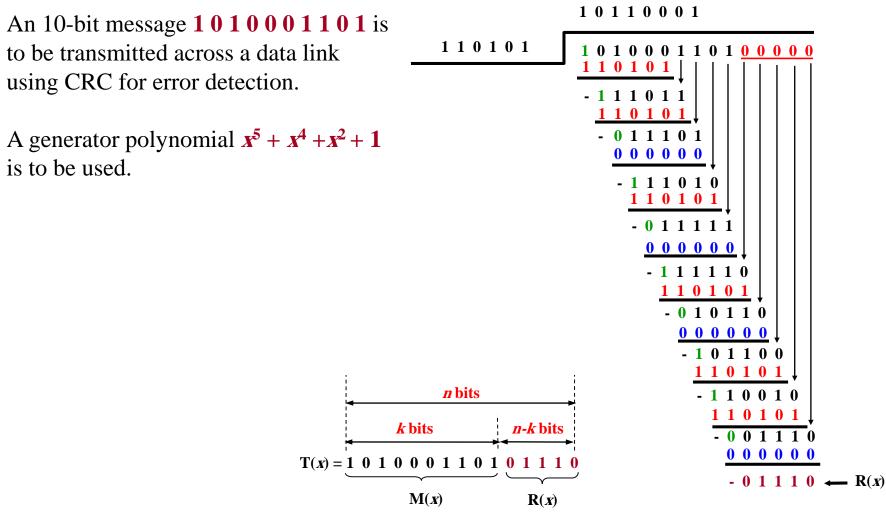

# Circuit with Shift Registers for Dividing by the Polynomial $X^5 + X^4 + X^2 + 1$

| An 10-bit message <b>1010001101</b> is                              | 10110001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| to be transmitted across a data link using CRC for error detection. | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| A generator polynomial $x^5 + x^4 + x^2 + 1$<br>is to be used.      | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                     | <i>n</i> bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Τ                                                                   | $(x) = \underbrace{\begin{array}{c} k \text{ bits} \\ 1 & 0 & 1 & 0 & 0 \\ 1 & 0 & 1 & 1 & 0 \\ 1 & 0 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 1 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 1 \\ 1 & 1 & 1 & 1 \\ 1 & 1 &$ |

William Stallings "Data and Computer Communications"

M(x)

$\mathbf{R}(\mathbf{x})$

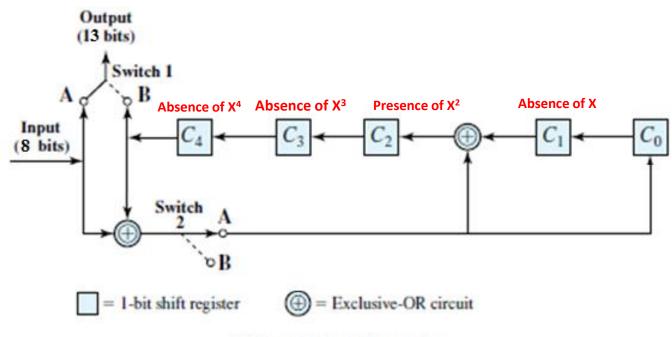

#### **Cyclic Redundancy Check General Implementation**

General CRC Architecture to Implement Divisor  $(1 + A_1X + A_2X^2 + \cdots + A_{n-1}X^{n-k-1} + X^{n-k})$

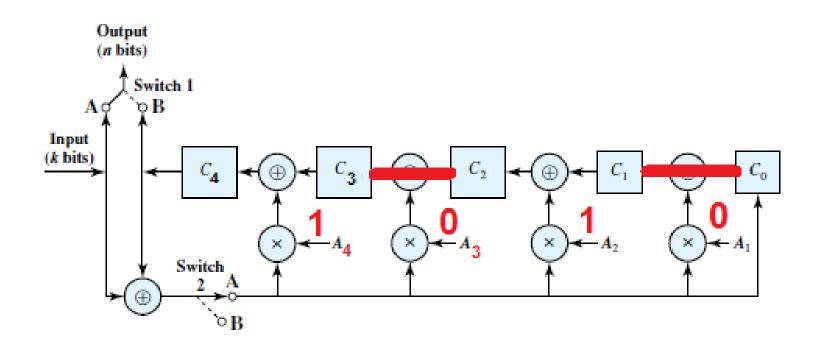

### Cyclic Redundancy Check General Implementation - Example

Generator Polynomial  $x^5 + x^4 + x^2 + 1$

#### **Error Correction**

# **Error Correction**

## **Error Correction**

Error detection is not always sufficient

wireless links have many errors

satellite links have long propagation delay

in both cases, retransmissions are expensive

#### **#Error-correcting codes**

add redundant bits to transmitted message

also known as forward error correction (FEC)

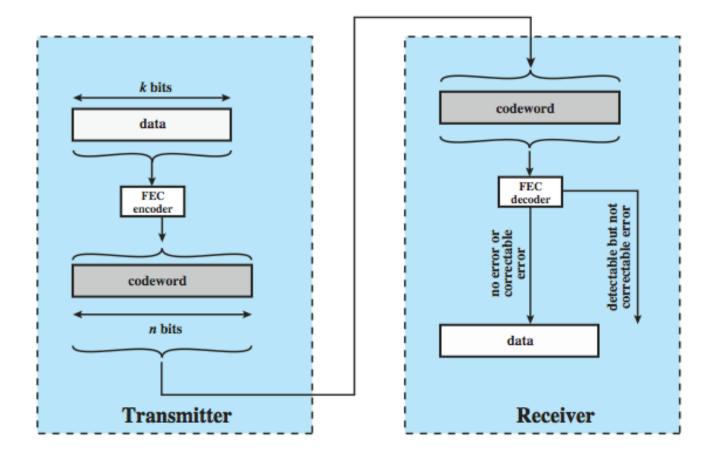

#### **Error Correction Process**

# **Error Correction – FEC Decoder**

- \* This block is passed through an FEC decoder, with one of four possible outcomes:

- **1.** If **there are no bit errors**, the input to the FEC decoder is identical to the original codeword, and the decoder produces the original data block as output.

- For certain error patterns, it is possible for the decoder to detect and correct those errors. Thus, even though the incoming data block differs from the transmitted codeword, the FEC decoder is able to map this block into the original data block.

- 3. For certain error patterns, the decoder can detect but not correct the errors. In this case, the decode simply reports an uncorrectable error.

- **4.** For certain, typically rare, error patterns, the decoder does not detect that any errors have occurred and maps the incoming *n*-bit data block into a *k*-bit block that differs from the original *k*-bit block.

## **How Error Correction Works**

**#**adds redundancy to transmitted message

**% can deduce original despite some errors**

Seg. block error correction code

Map k bit input onto an n bit codeword

Meach distinctly different

Mif get error assume codeword sent was closest to that received

**#**means have reduced effective data rate

## Codewords

#### **#** n bits total: k data bits, (n–k) redundant bits

- **⊮** 2<sup>n</sup> possible codewords

- **2**<sup>k</sup> valid codewords represent data

- Heratio of redundant bits to data bits, (n-k)/k is called the redundancy of the code

- **\*** The ratio of data bits to total bits,  $\frac{k}{n}$ , is called the **code rate**.

- For example, a code rate of 2/5 requires 2.5 times the capacity of an uncoded system. For example, if the data rate input to the encoder is 1 Mbps, then the output from the encoder must be at a rate of 2.5 Mbps to keep up.

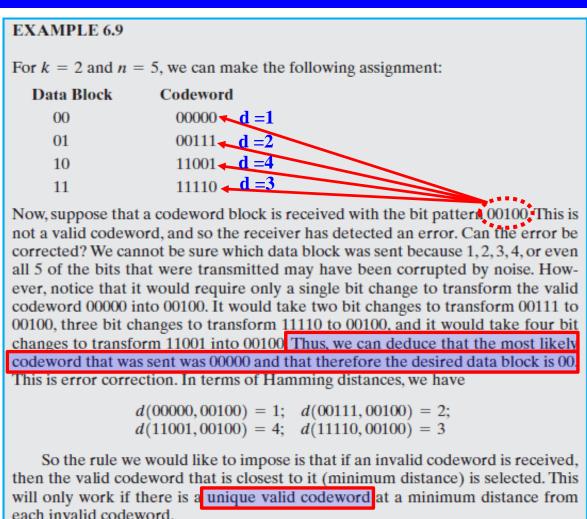

# Codewords Example:

# Codewords Example:

For our example, it is not true that for every invalid codeword there is one and only one valid codeword at a minimum distance. There are  $2^5 = 32$  possible codewords of which 4 are valid, leaving 28 invalid codewords. For the invalid codewords, we have the following:

| Invalid<br>Codeword | Minimum<br>Distance | Valid<br>Codeword | Invalid<br>Codeword | Minimum<br>Distance | Valid<br>Codeword |

|---------------------|---------------------|-------------------|---------------------|---------------------|-------------------|

| 00001               | 1                   | 00000             | 10000               | 1                   | 00000             |

| 00010               | 1                   | 00000             | 10001               | 1                   | 11001             |

| 00011               | 1                   | 00111             | 10010               | 2                   | 00000 or 11110    |

| 00100               | 1                   | 00000             | 10011               | 2                   | 00111 or 11001    |

| 00101               | 1                   | 00111             | 10100               | 2                   | 00000 or 11110    |

| 00110               | 1                   | 00111             | 10101               | 2                   | 00111 or 11001    |

| 01000               | 1                   | 00000             | 10110               | 1                   | 11110             |

| 01001               | 1                   | 11001             | 10111               | 1                   | 00111             |

| 01010               | 2                   | 00000 or 11110    | 11000               | 1                   | 11001             |

| 01011               | 2                   | 00111 or 11001    | 11010               | 1                   | 11110             |

| 01100               | 2                   | 00000 or 11110    | 11011               | 1                   | 11001             |

| 01101               | 2                   | 00111 or 11001    | 11100               | 1                   | 11110             |

| 01110               | 1                   | 11110             | 11101               | 1                   | 11001             |

| 01111               | 1                   | 00111             | 11111               | 1                   | 11110             |

|                     |                     |                   |                     |                     |                   |

# Codewords Example:

There are eight cases in which an invalid codeword is at a distance 2 from two different valid codewords. Thus, if one such invalid codeword is received, an error in 2 bits could have caused it and the receiver has no way to choose between the two alternatives. An error is detected but cannot be corrected. However, in every case in which a single bit error occurs, the resulting codeword is of distance 1 from only one valid codeword and the decision can be made. This code is therefore capable of correcting all single-bit errors but cannot correct double bit errors. Another way to see this is to look at the pairwise distances between valid codewords:

d(00000, 00111) = 3; d(00000, 11001) = 3; d(00000, 11110) = 4;d(00111, 11001) = 4; d(00111, 11110) = 3; d(11001, 11110) = 3;

The minimum distance between valid codewords is 3. Therefore, a single bit error will result in an invalid codeword that is a distance 1 from the original valid codeword but a distance at least 2 from all other valid codewords. As a result, the code can always correct a single-bit error. Note that the code also will always detect a double-bit error.

# **Hamming Distance**

**%** Number of different bits between two codewords

**#** Calculated using bitwise XOR, counting 1s

#### **# Example** $v_1 = 011011, v_2 = 110001$ $v_1 \oplus v_2 = 101010, d(v_1, v_2) = 3$

#### **#** Minimum distance

rightarrow for code consisting of w<sub>1</sub>, w<sub>2</sub>, ..., w<sub>s</sub>, s = 2<sup>n</sup>rightarrow d<sub>min</sub> = min <sub>i≠j</sub> [d(w<sub>i</sub>, w<sub>j</sub>)]

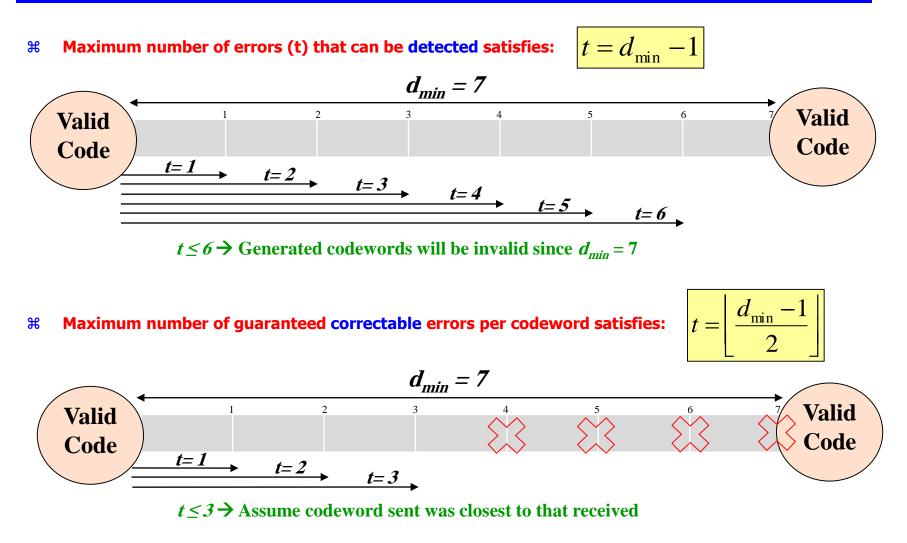

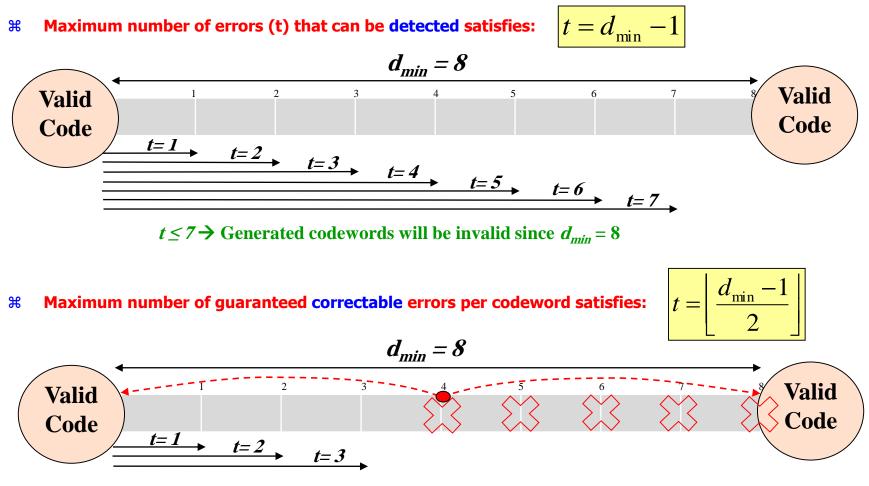

# **Hamming Distance**

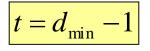

**#** Maximum number of errors (t) that can be detected satisfies:

$t = d_{\min} - 1$

**X** Maximum number of guaranteed correctable errors per codeword satisfies:

$$t = \left\lfloor \frac{d_{\min} - 1}{2} \right\rfloor$$

with t single bit errors, resulting codeword is still closer to one of the valid codewords

## **Hamming Distance - Example**

## **Hamming Distance - Example**

$t \leq 3 \rightarrow$  Assume codeword sent was closest to that received

### **Hamming Distance**

**#** The design of a block code involves a number of considerations:

**1.** For given values of *n* and *k*, we would like the **largest possible** value of d<sub>min</sub>.

**2.** The code should be relatively easy to encode and decode, requiring minimal memory and processing time.

3. We would like the number of extra bits, (*n* - *k*), to be small, to reduce bandwidth.

4. We would like the number of extra bits , (*n* - *k*), to be large, to reduce error rate.

Clearly, the last two objectives are in conflict, and **tradeoffs** must be made.

Dr. Mohammed Arafah

### Hamming Distance - Example 1

% Valid codewords: 000000, 000111, 111000, 111111

# Hamming distance = 3

```

% Can detect up to 2 errors

% 000011, 000110, 100100, 100001

% 001111, 000110, 110111, 101111 Discard

% 110011, 011110, 101101, 111100

```

### Hamming Distance - Example 2

###

# Hamming distance = 5

**#** Can **correct** up to 2 errors

# 000000011, 000000101 → 000000000 # 000000111, 0001111111 → 0000011111

# Single Error Correction Hamming Code

It is a code with *m* message bit and *r* parity bits that will allow all single errors to be corrected.

### **Transmitter:**

- He bits that are powers of 2 (1, 2, 4, 8, 16, etc.) are parity bits.

The rest (3, 5, 6, 7, 9, etc.) are filled up the *m* data bits.

- The parity bits are calculated such that we make (c1=c2=c4=...=0)

according to the following equations:

$$c_{1} = p_{1} \oplus m_{3} \oplus m_{5} \oplus m_{7} \oplus m_{9} \oplus m_{11} \oplus \dots$$

$$c_{2} = p_{2} \oplus m_{3} \oplus m_{6} \oplus m_{7} \oplus m_{9} \oplus m_{10} \oplus \dots$$

$$c_{4} = p_{4} \oplus m_{5} \oplus m_{6} \oplus m_{7} \oplus m_{12} \oplus m_{13} \oplus \dots$$

$$c_{8} = p_{8} \oplus m_{9} \oplus m_{10} \oplus m_{11} \oplus m_{12} \oplus m_{13} \oplus \dots$$

# Single Error Correction Hamming Code

### **Receiver:**

$$c_{1} = p_{1} \oplus m_{3} \oplus m_{5} \oplus m_{7} \oplus m_{9} \oplus m_{11} \oplus \dots$$

$$c_{2} = p_{2} \oplus m_{3} \oplus m_{6} \oplus m_{7} \oplus m_{9} \oplus m_{10} \oplus \dots$$

$$c_{4} = p_{4} \oplus m_{5} \oplus m_{6} \oplus m_{7} \oplus m_{12} \oplus m_{13} \oplus \dots$$

$$c_{8} = p_{8} \oplus m_{9} \oplus m_{10} \oplus m_{11} \oplus m_{12} \oplus m_{13} \oplus \dots$$

.....

If (c1=c2=c4=c8=...=0), then the codeword is received correctly. Otherwise, the values of the check bits are used to determine the location of the error in the codeword.

# Indle Error Correction Hamming Code – Example 1:

Assuming that the transmitted character **'C'**, generate the Hamming codeword.

#### 'C' = 11000011

| <b>P</b> <sub>1</sub> | <b>P</b> <sub>2</sub> | <b>m</b> <sub>3</sub> | <b>P</b> <sub>4</sub> | <b>m</b> <sub>5</sub> | m <sub>6</sub> | <b>m</b> <sub>7</sub> | <b>P</b> <sub>8</sub> | m <sub>9</sub> | <b>m</b> <sub>10</sub> | <b>m</b> <sub>11</sub> | <b>m</b> <sub>12</sub> |

|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|----------------|-----------------------|-----------------------|----------------|------------------------|------------------------|------------------------|

| ?                     | ?                     | 1                     | ?                     | 1                     | 0              | 0                     | ?                     | 0              | 0                      | 1                      | 1                      |

|                       |                       |                       |                       |                       |                | -                     |                       | -              | <b>101</b> 0           |                        |                        |

#### **Solution of Example 1:**

$$C_{1} = P_{1} \oplus m_{3} \oplus m_{5} \oplus m_{7} \oplus m_{9} \oplus m_{11}$$

$$\Rightarrow C_{1} = ? \oplus 1 \oplus 1 \oplus 0 \oplus 0 \oplus 1$$

$$C_{1} = 0 \Rightarrow P_{1} = 1$$

$$C_{2} = P_{2} \oplus m_{3} \oplus m_{6} \oplus m_{7} \oplus m_{10} \oplus m_{11}$$

$$\Rightarrow C_{2} = ? \oplus 1 \oplus 0 \oplus 0 \oplus 0 \oplus 1$$

$$C_{2} = 0 \Rightarrow P_{2} = 0$$

$$C_{4} = P_{4} \oplus m_{5} \oplus m_{6} \oplus m_{7} \oplus m_{12}$$

$$\Rightarrow C_{4} = ? \oplus 1 \oplus 0 \oplus 0 \oplus 1$$

$$C_{4} = 0 \Rightarrow P_{4} = 0$$

$$C_{8} = P_{8} \oplus m_{9} \oplus m_{10} \oplus m_{11} \oplus m_{12}$$

$$\Rightarrow C_{8} = ? \oplus 0 \oplus 0 \oplus 1 \oplus 1$$

$$C_{8} = 0 \Rightarrow P_{8} = 0$$

$$\Rightarrow The transmitted Hamming codeword is:$$

# Single Error Correction Hamming Code – Example 2:

Assuming that the transmitted character 'M', generate the Hamming codeword.

#### 'M' = 11010100

| <b>P</b> <sub>1</sub> | <b>P</b> <sub>2</sub> | <b>m</b> <sub>3</sub> | <b>P</b> <sub>4</sub> | <b>m</b> <sub>5</sub> | m <sub>6</sub> | <b>m</b> <sub>7</sub> | <b>P</b> <sub>8</sub> | m <sub>9</sub> | <b>m</b> <sub>10</sub> | <b>m</b> <sub>11</sub> | <b>m</b> <sub>12</sub> |

|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|----------------|-----------------------|-----------------------|----------------|------------------------|------------------------|------------------------|

| ?                     | ?                     | 0                     | ?                     | 0                     | 1              | 0                     | ?                     | 1              | 0                      | 1                      | 1                      |

| <b>0001</b>           | 00 <b>1</b> 0         | 0011                  | 0100                  | 0101                  | 0110           | 0111                  | 1000                  | 1001           | <b>101</b> 0           | 1011                   | 1100                   |

**Solution of Example 2:**

$C_1 = P_1 \oplus m_3 \oplus m_5 \oplus m_7 \oplus m_9 \oplus m_{11}$  $\rightarrow$  C<sub>1</sub> = ?  $\oplus$  0  $\oplus$  0  $\oplus$  0  $\oplus$  1  $\oplus$  1  $C_1 = 0 \rightarrow P_1 = 0$  $C_2 = P_2 \oplus m_3 \oplus m_6 \oplus m_7 \oplus m_{10} \oplus m_{11}$  $\rightarrow$  C<sub>2</sub> = ?  $\oplus$  0  $\oplus$  1  $\oplus$  0  $\oplus$  0  $\oplus$  1  $C_2 = 0 \rightarrow P_2 = 0$  $C_4 = P_4 \oplus m_5 \oplus m_6 \oplus m_7 \oplus m_{12}$  $\rightarrow$  C<sub>4</sub> = ?  $\oplus$  0  $\oplus$  1  $\oplus$  0  $\oplus$  1  $C_4 = 0 \rightarrow P_4 = 0$  $\mathbf{C}_8 = \mathbf{P}_8 \oplus \mathbf{m}_9 \oplus \mathbf{m}_{10} \oplus \mathbf{m}_{11} \oplus \mathbf{m}_{12}$  $\rightarrow C_8 = ? \oplus 1 \oplus 0 \oplus 1 \oplus 1$  $C_8 = 0 \rightarrow P_8 = 1$  $\rightarrow$  The transmitted Hamming codeword is: 0 0 0 0 0 1 0 1 0 1 1 1

# Single Error Correction Hamming Code – Example 3:

#### The received Hamming codeword is:

| <b>P</b> <sub>1</sub> | <b>P</b> <sub>2</sub> | m <sub>3</sub> | <b>P</b> <sub>4</sub> | <b>m</b> <sub>5</sub> | m <sub>6</sub> | <b>m</b> <sub>7</sub> | <b>P</b> <sub>8</sub> | m <sub>9</sub> | <b>m</b> <sub>10</sub> | <b>m</b> <sub>11</sub> | <b>m</b> <sub>12</sub> |

|-----------------------|-----------------------|----------------|-----------------------|-----------------------|----------------|-----------------------|-----------------------|----------------|------------------------|------------------------|------------------------|

| 1                     | 0                     | 1              | 0                     | 0                     | 0              | 1                     | 1                     | 0              | 1                      | 1                      | 1                      |

| 0001                  | 0010                  | 0011           | 0100                  | 0101                  | 0110           | 0111                  | 1000                  | 1001           | 1010                   | 1011                   | 1100                   |

Deduce the correct character from the above codeword after correction any error, if any.

#### **Conclusion:**

- $\rightarrow$  The codeword is correct

- → The codeword is **101000110111**

- $\rightarrow$  The message is 11101001

- $\rightarrow$  The EBCDIC character is Z

#### **Solution of Example 3:**

```

C_1 = P_1 \oplus m_3 \oplus m_5 \oplus m_7 \oplus m_9 \oplus m_{11}

\rightarrow C_1 = 1 \oplus 1 \oplus 0 \oplus 1 \oplus 0 \oplus 1

\rightarrow C_1 = 0

C_2 = P_2 \oplus m_3 \oplus m_6 \oplus m_7 \oplus m_{10} \oplus m_{11}

\rightarrow C<sub>2</sub> = 0 \oplus 1 \oplus 0 \oplus 1 \oplus 1 \oplus 1

\rightarrow C<sub>2</sub> = 0

C_4 = P_4 \oplus m_5 \oplus m_6 \oplus m_7 \oplus m_{12}

\mathbf{i} \mathbf{C}_4 = \mathbf{0} \oplus \mathbf{0} \oplus \mathbf{0} \oplus \mathbf{1} \oplus \mathbf{1}

\rightarrow C_4 = 0

C_8 = P_8 \oplus m_9 \oplus m_{10} \oplus m_{11} \oplus m_{12}

\rightarrow C_8 = 1 \oplus 0 \oplus 1 \oplus 1 \oplus 1

\rightarrow C_8 = 0

C_8 C_4 C_2 C_1

0

0

0

0

```

# Single Error Correction Hamming Code – Example 4:

#### The received Hamming codeword is:

| <b>P</b> <sub>1</sub> | <b>P</b> <sub>2</sub> | <b>m</b> <sub>3</sub> | <b>P</b> <sub>4</sub> | <b>m</b> <sub>5</sub> | m <sub>6</sub> | <b>m</b> <sub>7</sub> | <b>P</b> <sub>8</sub> | m <sub>9</sub> | <b>m</b> <sub>10</sub> | <b>m</b> <sub>11</sub> | <b>m</b> <sub>12</sub> |

|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|----------------|-----------------------|-----------------------|----------------|------------------------|------------------------|------------------------|

| 0                     | 0                     | 1                     | 1                     | 0                     | 0              | 0                     | 0                     | 0              | 0                      | 0                      | 1                      |

| 0001                  | 0010                  | 0011                  | 0100                  | 0101                  | 0110           | 0111                  | 1000                  | 1001           | 1010                   | 1011                   | 1100                   |

Deduce the correct character from the above codeword after correction any error, if any.

#### **Conclusion:**

- $\rightarrow$  m<sub>11</sub> is incorrect

- $\rightarrow$  m<sub>11</sub> must be 1

- $\rightarrow$  The codeword is 0 0 1 1 0 0 0 0 0 (1)1

- $\rightarrow$  The message is 1100001

- → The EBCDIC character is A

### Solution of Example 4:

```

C_1 = P_1 \oplus m_3 \oplus m_5 \oplus m_7 \oplus m_9 \oplus m_{11}

\rightarrow C<sub>1</sub> = 0 \oplus 1 \oplus 0 \oplus 0 \oplus 0 \oplus 0

\rightarrow C<sub>1</sub> = 1

C_2 = P_2 \oplus m_3 \oplus m_6 \oplus m_7 \oplus m_{10} \oplus m_{11}

\rightarrow C<sub>2</sub> = 0 \oplus 1 \oplus 0 \oplus 0 \oplus 0 \oplus 0

\rightarrow C<sub>2</sub> = 1

C_4 = P_4 \oplus m_5 \oplus m_6 \oplus m_7 \oplus m_{12}

\rightarrow C<sub>4</sub> = 1 \oplus 0 \oplus 0 \oplus 0 \oplus 1

\rightarrow C_4 = 0

C_8 = P_8 \oplus m_9 \oplus m_{10} \oplus m_{11} \oplus m_{12}

\rightarrow C_8 = 0 \oplus 0 \oplus 0 \oplus 0 \oplus 1

\rightarrow C_8 = 1

C_8 C_4 C_2 C_1

1 0 1 1

```

# Single Error Correction Hamming Code – Example 5:

The received Hamming codeword is:

| <b>P</b> <sub>1</sub> | <b>P</b> <sub>2</sub> | m <sub>3</sub> | <b>P</b> <sub>4</sub> | <b>m</b> <sub>5</sub> | m <sub>6</sub> | <b>m</b> <sub>7</sub> | <b>P</b> <sub>8</sub> | m <sub>9</sub> | <b>m</b> <sub>10</sub> | <b>m</b> <sub>11</sub> | <b>m</b> <sub>12</sub> |

|-----------------------|-----------------------|----------------|-----------------------|-----------------------|----------------|-----------------------|-----------------------|----------------|------------------------|------------------------|------------------------|

| 0                     | 0                     | 1              | 0                     | 1                     | 0              | 1                     | 0                     | 1              | 1                      | 1                      | 1                      |

| 0001                  | 0010                  | 0011           | 0100                  | 0101                  | 0110           | 0111                  | 1000                  | 1001           | 1010                   | 1011                   | 1100                   |

Deduce the correct character from the above codeword after correction any error, if any.

### **Conclusion:**

$\rightarrow$  m<sub>5</sub> is incorrect

- $\rightarrow$  m<sub>5</sub> must be 0

- $\rightarrow$  The message is 11111001

- → The EBCDIC character is 9

### **Solution of Example 5:**

```

C_1 = P_1 \oplus m_3 \oplus m_5 \oplus m_7 \oplus m_9 \oplus m_{11}

\rightarrow C<sub>1</sub> = 0 \oplus 1 \oplus 1 \oplus 1 \oplus 1 \oplus 1 \oplus 1

\rightarrow C<sub>1</sub> = 1

C_2 = P_2 \oplus m_3 \oplus m_6 \oplus m_7 \oplus m_{10} \oplus m_{11}

\rightarrow C<sub>2</sub> = 0 \oplus 1 \oplus 0 \oplus 1 \oplus 1 \oplus 1

\rightarrow C<sub>2</sub> = 0

C_4 = P_4 \oplus m_5 \oplus m_6 \oplus m_7 \oplus m_{12}

\rightarrow C<sub>4</sub> = 0 \oplus 1 \oplus 0 \oplus 1 \oplus 1

\rightarrow C_4 = 1

C_8 = P_8 \oplus m_9 \oplus m_{10} \oplus m_{11} \oplus m_{12}

\rightarrow C_8 = 0 \oplus 1 \oplus 1 \oplus 1 \oplus 1 \oplus 1

\rightarrow C_8 = 0

C_8 C_4 C_2 C_1

```

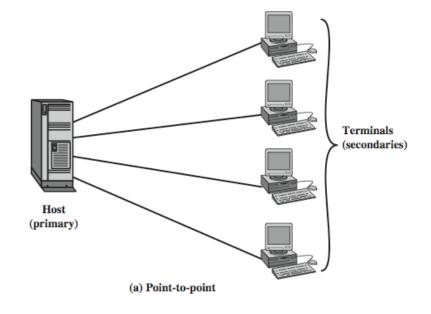

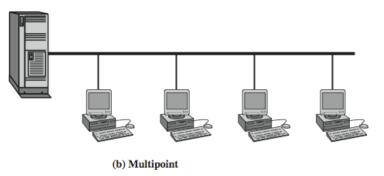

# **Line Configuration - Topology**

physical arrangement of stations

on medium

point to point - two stations

Such as between two routers / computers

multi point - multiple stations

Itraditionally mainframe computer and terminals

**#** classify data exchange as half or full duplex

half duplex (two-way alternate)

Image: Only one station may transmit at a time

Image: Provide the state of the state o

**# full duplex** (two-way simultaneous)

simultaneous transmission and reception between two stations

requires two data paths

Separate media or frequencies used for each direction

### Summary

# asynchronous verses synchronous transmission # error detection and correction # line configuration issues